# 3

---

## Die digitale logische Ebene

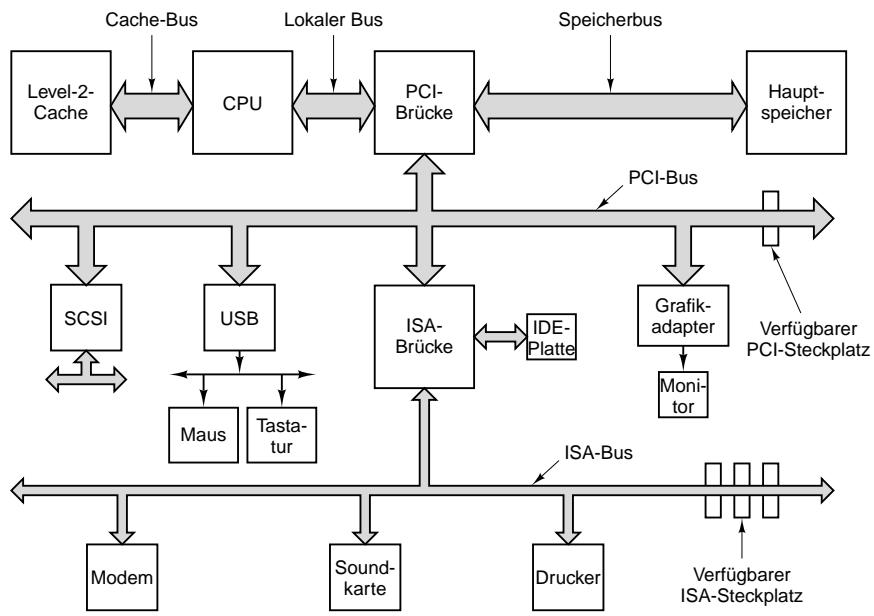

Unten in der Hierarchie von Abb. 1.2 liegt die digitale logische Ebene – die echte Computer-Hardware. In diesem Kapitel untersuchen wir viele Aspekte der digitalen Logik als Baustein für die Studie der höheren Ebenen, die in späteren Kapiteln behandelt werden. Dieses Thema liegt an der Grenze zwischen Informatik und Elektrotechnik. Der Stoff wird aber in sich geschlossen und selbsterklärend vorgestellt, so daß keine Kenntnisse über Hardware oder Technik erforderlich sind.

Die Grundelemente, aus denen alle digitalen Computer gebaut werden, sind erstaunlich einfach. Wir beginnen unsere Untersuchung mit einer Betrachtung dieser Grundelemente und der speziellen, zweiwertigen Algebra (boolesche Algebra), die zur Analyse dieser Elemente benutzt wird. Anschließend untersuchen wir einige grundlegenden Schaltungen, die mit Hilfe von Gates in einfachen Kombinationen gebaut werden können, darunter Schaltungen für die Durchführung von Arithmetik. Das nächste Thema ist die Kombination von Gates, um Informationen zu speichern, d.h. Speicherorganisation. Danach befassen wir uns mit dem Thema »CPU«, insbesondere damit, wie Einzelchip-CPUs Daten mit Speichern und Peripheriegeräten austauschen. Zahlreiche Beispiele aus der Industrie werden in späteren Abschnitten dieses Kapitels betrachtet.

### 3.1 Gates und boolesche Algebra

Digitale Schaltungen lassen sich aus einer kleinen Zahl von primitiven Elementen bauen, indem man diese auf vielfache Art und Weise kombiniert. In den folgenden Abschnitten werden diese primitiven Elemente beschrieben. Außerdem wird erklärt, wie sie sich kombinieren lassen. Es wird weiter eine mächtige mathematische Methode vorgestellt, mit der man das Verhalten dieser Elemente analysieren kann.

#### 3.1.1 Gates

Bei einer digitalen Schaltung gibt es nur zwei logische Werte. Normalerweise stellt ein Signal zwischen 0 und 1 Volt einen Wert (z.B. eine binäre 0) und ein Signal zwischen 2 und 5 Volt einen anderen Wert (z.B. eine binäre 1) dar. Spannungen außerhalb dieser beiden Bereiche sind nicht zulässig. Winzige elektronische Geräte namens **Gates** (Gatter) können mit diesen zweiwertigen Signalen verschiedene Funktionen berechnen. Diese Gates bilden die Hardware-Grundlage, auf der alle digitalen Computer basieren.

Die Einzelheiten darüber, wie diese Gates im Innern funktionieren, sind nicht Gegenstand dieses Buchs, sondern gehören zur **Geräteebene** (Device Level),

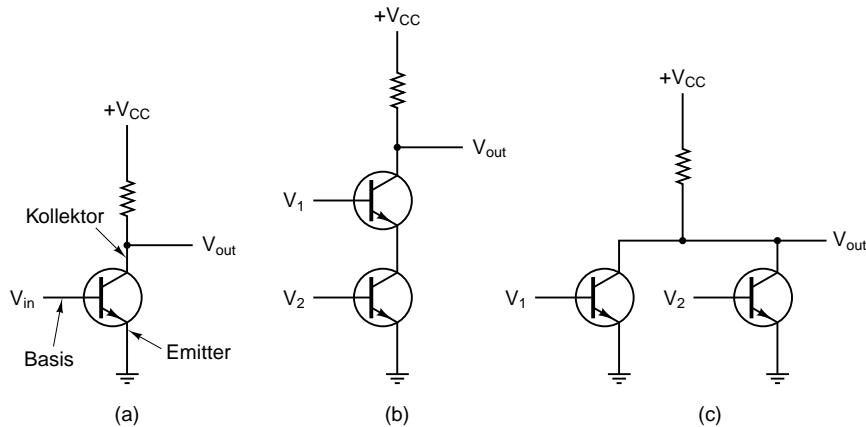

die unterhalb unserer Ebene 0 liegt. Wir schweifen jetzt aber dennoch kurz ab und werfen einen kurzen Blick auf das – einfache – Grundkonzept. Jede moderne digitale Logik beruht letztendlich auf der Tatsache, daß ein Transistor so gebaut werden kann, daß er als sehr schneller, binärer Schalter arbeitet. In Abb. 3.1(a) ist ein einzelner bipolarer Transistor (der Kreis) in eine einfache Schaltung eingebettet. Dieser Transistor hat drei Verbindungen mit der Außenwelt: den **Kollektor**, die **Basis** und den **Emitter**. Liegt die Eingangsspannung  $V_{in}$  unter einem bestimmten kritischen Wert, schaltet sich der Transistor aus und verhält sich wie ein unendlicher Widerstand. Dies veranlaßt den Ausgang der Schaltung  $V_{out}$ , einen Wert nahe  $V_{cc}$  – eine extern geregelte Spannung – anzunehmen, die normalerweise bei diesem Transistortyp bei +5 Volt liegt. Überschreitet  $V_{in}$  den kritischen Wert, schaltet sich der Transistor ein und funktioniert wie ein Draht, wodurch  $V_{out}$  nach unten zur Masse (gemäß Konvention 0 Volt) gezogen wird.

Abb. 3.1: (A) Transistor-Inverter; (b) NAND-Gate; (c) NOR-Gate

Wichtig dabei ist folgendes: Wenn  $V_{in}$  auf Low liegt, liegt  $V_{out}$  auf High, und umgekehrt. Folglich ist diese Schaltung ein Inverter, der eine logische 0 in eine logische 1 und eine logische 1 in eine logische 0 konvertiert. Der Widerstand (Resistor) – die gezackte Linie – ist nötig, um den vom Transistor gezogenen Strom zu begrenzen. Die Zeit, die benötigt wird, um von einem Zustand in den anderen umzuschalten, beträgt normalerweise ein paar Nanosekunden.

Abb. 3.1(b) zeigt zwei in Reihe geschaltete Transistoren. Liegen  $V_1$  und  $V_2$  auf High, leiten beide Transistoren, und  $V_{out}$  wird nach unten gezogen. Liegt einer der beiden Eingänge auf Low, schaltet der entsprechende Transistor aus, und der Ausgang geht auf High. Anders ausgedrückt:  $V_{out}$  ist auf Low, aber nur dann, wenn sowohl  $V_1$  als auch  $V_2$  auf High liegen.

Die beiden Transistoren in Abb. 3.1(c) sind nicht in Reihe, sondern parallel geschaltet. Liegt einer der Eingänge in dieser Konfiguration auf High, schaltet

der entsprechende Transistor ein und zieht den Ausgang nach unten zur Masse. Sind beide Eingänge auf Low, bleibt der Ausgang auf High.

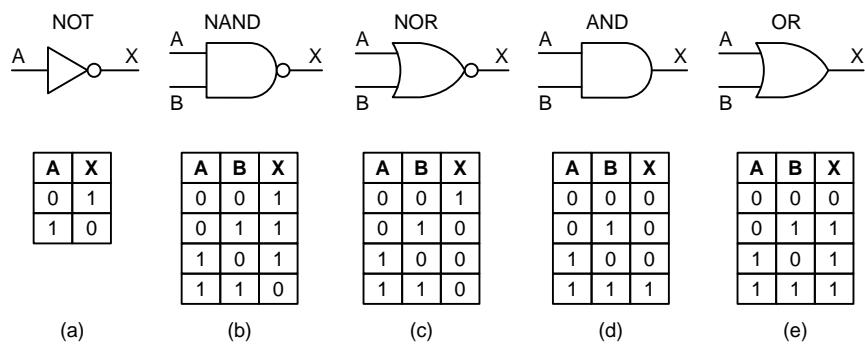

Diese drei Schaltungen bzw. ihre Gegenstücke bilden die drei einfachsten Gates. Sie heißen NOT, NAND und NOR. NOT-Gates nennt man oft **Inverter**. Wir benutzen die beiden Begriffe als Synonyme. Wenden wir nun die Konvention an, daß »High« ( $V_{cc}$  Volt) eine logische 1 und »Low« (Masse) eine logische 0 ist, können wir den Ausgangswert als Funktion der Eingangswerte ausdrücken. Abb. 3.2(a) bis (c) zeigt die üblicherweise für die Darstellung dieser drei Gates benutzten Symbole und die Funktion der einzelnen Schaltungen. In diesen Abbildungen sind  $A$  und  $B$  Eingänge, und  $X$  ist der Ausgang. Jede Reihe legt den Ausgang für eine unterschiedliche Kombination von Eingängen fest.

Abb. 3.2: Symbole und funktionales Verhalten der fünf grundlegenden Gates

Wird das Ausgangssignal von Abb. 3.1(b) in eine Inverter-Schaltung eingespeist, erhalten wir eine weitere Schaltung mit genau dem Gegenteil des NAND-Gates, d.h. eine Schaltung, deren Ausgang 1 ist, wenn beide Eingänge 1 sind. Eine solche Schaltung nennt man AND-Gate. Abb. 3.2(d) zeigt das entsprechende Symbol und die funktionale Beschreibung. Ebenso kann das NOR-Gate mit einem Inverter verbunden werden, um eine Schaltung zu erzielen, deren Ausgang 1 ist, wenn entweder einer oder beide Eingänge 1 sind, aber 0 ist, wenn beide Eingänge 0 sind. Das Symbol und die funktionale Beschreibung dieser Schaltung, die man »OR-Gate« nennt, sind in Abb. 3.2(e) dargestellt. Die kleinen Kreise in den Symbolen des Inverters, des NAND-Gates und des NOR-Gates nennt man **Inversionsblasen** (Inversion Bubbles). Sie werden häufig auch in anderen Zusammenhängen benutzt, um ein invertiertes Signal zu bezeichnen.

Die fünf Gates von Abb. 3.2 sind die grundlegenden Bausteine der digitalen logischen Ebene. Aus der vorhergehenden Darstellung wird klar, daß das NAND- und NOR-Gate je zwei Transistoren benötigen, während das AND- und OR-Gate jeweils drei braucht. Aus diesem Grund basieren viele Computer auf NAND- und NOR-Gates, und nicht auf den bekannteren AND- und OR-Gates. (In der Praxis werden alle Gates etwas anders implementiert, NAND und NOR sind aber dennoch einfacher als AND und OR.) Nebenbei bemerkt, können

Gates mehr als zwei Eingänge haben. Im Prinzip kann beispielsweise ein NAND-Gate beliebig viele Eingänge haben. In der Praxis sind aber mehr als acht Eingänge ungewöhnlich.

Obwohl die Konstruktion von Gates zur Geräteebene gehört, werden hier die wichtigen Herstellungstechnologien erwähnt, auf die häufig Bezug genommen wird. Die beiden wichtigsten Technologien sind **bipolar** und **MOS** (Metal Oxide Semiconductor). Die wichtigen bipolaren Typen sind **TTL** (Transistor-Transistor Logic) – seit Jahren das Arbeitspferd der digitalen Elektronik – und **ECL** (Emitter-Coupled Logic), die benutzt wird, wenn sehr hohe Geschwindigkeiten gefordert werden.

MOS-Gates sind langsamer als TTL und ECL, erfordern aber weniger Strom und nehmen viel weniger Platz ein. Deshalb können sie in großer Zahl auf engem Raum gepackt werden. MOS gibt es in vielen Varianten, darunter PMOS, NMOS und CMOS. Während MOS-Transistoren anders als bipolare Transistoren gebaut werden, ist ihre Fähigkeit, als elektronische Schalter zu funktionieren, gleich. Die meisten modernen CPUs und Speicher basieren auf der CMOS-Technologie, die mit +3,3 Volt läuft. Das ist alles, was wir über die Geräteebene festhalten wollen. Leser, die an dieser Ebene interessiert sind, finden einschlägige Literaturhinweise in Kapitel 9.

### 3.1.2 Boolesche Algebra

Um die Schaltungen zu beschreiben, die durch Kombination von Gates gebaut werden können, ist eine neue Art von Algebra erforderlich – eine, bei der Variablen und Funktionen nur die Werte 0 und 1 annehmen können. Eine solche Algebra nennt man **boolesche Algebra** nach ihrem Begründer, dem englischen Mathematiker George Boole (1815–1864). Genau genommen haben wir es hier eigentlich mit einer bestimmten Art von boolescher Algebra zu tun, einer **Schaltalgebra** (Switching Algebra). Der Begriff »boolesche Algebra« hat sich aber stark eingebürgert, so daß wir hier ebenfalls nicht unterscheiden.

Genauso, wie es Funktionen in der »Schulalgebra« gibt, kennt man Funktionen in der booleschen Algebra. Eine boolesche Funktion hat eine oder mehrere EingabevARIABLEN und führt zu einem Ergebnis, das nur von den Werten dieser Variablen abhängt. Eine einfache Funktion  $f$  lässt sich wie folgt definieren:  $f(A)$  ist 1, wenn  $A = 0$  ist und  $f(A)$  ist 0, wenn  $A = 1$  ist. Dies ist die NOT-Funktion von Abb. 3.2(a).

Da eine boolesche Funktion mit  $n$  Variablen nur  $2^n$  mögliche Kombinationen von Eingabewerten hat, kann man die Funktion vollständig beschreiben, indem man eine Tabelle mit  $2^n$  Reihen angibt, wobei jede Reihe den Wert der Funktion für eine andere Kombination von Eingangswerten angibt. Eine solche Tabelle heißt **Wahrheitstabelle** (Truth Table). Die Tabellen in Abb. 3.2 geben Beispiele. Wollen wir uns darauf festlegen, die Reihen einer Wahrheitstabelle immer in numerischer Reihenfolge (Basis 2) anzurufen. Für zwei Variablen in der Reihenfolge 00, 01, 10 und 11 kann dann also die Funktion

vollständig mit der  $2^n$ -Bit-Binärzahl beschrieben werden, die wir erhalten, wenn wir die Ergebnisspalte der Wahrheitstabelle vertikal lesen. Das heißt: NAND ist 1110, NOR ist 1000, AND ist 0001 und OR ist 0111. Selbstverständlich gibt es nur 16 boolesche Funktionen von zwei Variablen, entsprechend den 16 möglichen 4-Bit-Ergebnisketten. Demgegenüber verfügt die gewöhnliche Algebra über eine unendliche Zahl an Funktionen von zwei Variablen, von denen sich keine dadurch beschreiben lässt, daß man eine Tabelle mit Ausgängen für alle möglichen Eingänge schreibt, weil jede Variable jeden beliebigen einer unendlichen Zahl möglicher Werte annehmen kann.

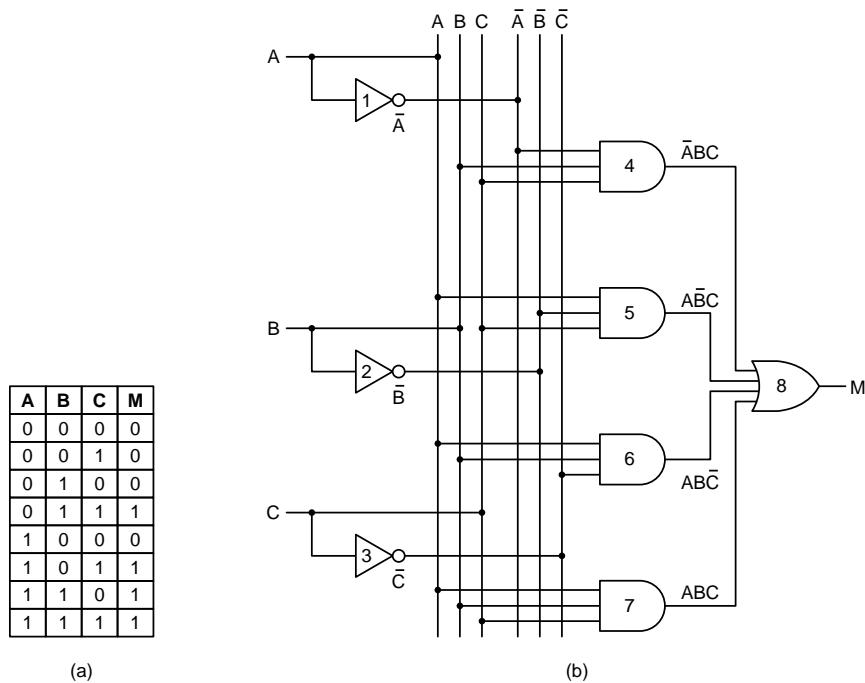

Abb. 3.3(a) zeigt die Wahrheitstabelle für eine boolesche Funktion von drei Variablen:  $M = f(A, B, C)$ . Diese Funktion ist die logische Mehrheitsfunktion. Das heißt, sie ist 0, wenn eine Mehrheit ihrer Eingänge 0 ist, und 1, wenn eine Mehrheit ihrer Eingänge 1 ist. Obwohl man jede boolesche Funktion vollständig mit Hilfe einer Wahrheitstabelle festlegen kann, wird diese Notation zunehmend mühsamer, je höher die Anzahl der Variablen ist. Deshalb wird häufig eine andere Notation benutzt.

Abb. 3.3: (a) Die Wahrheitstabelle der Mehrheitsfunktion von drei Variablen; (b) eine Schaltung für (a)

Um zu sehen, wie diese andere Notation entstanden ist, beachte man, daß jede boolesche Funktion dadurch festgelegt werden kann, daß man sagt, welche Kombinationen von Eingangsvariablen einen Ausgangswert von 1 ergeben.

Für die Funktion von Abb. 3.3(a) gibt es vier Kombinationen von Eingangsvariablen, die  $M$  den Wert 1 annehmen lassen. Der Konvention entsprechend schreiben wir die Eingangsvariablen mit einem Überstrich, um anzudeuten, daß ihr Wert invertiert ist. Fehlt der Überstrich, bedeutet das einen nicht invertierten Wert. Außerdem verwenden wir eine implizierte Multiplikation bzw. einen Punkt, um ein gemitteltes AND anzudeuten, und ein Pluszeichen (+) für ein gemitteltes OR. Das heißt z.B., daß  $\bar{A}\bar{B}C$  nur dann den Wert 1 annimmt, wenn  $A = 1$  und  $B = 0$  und  $C = 1$ .  $\bar{A}\bar{B} + \bar{B}\bar{C}$  ist nur 1, wenn ( $A = 1$  und  $B = 0$ ) oder ( $B = 1$  und  $C = 0$ ). Die vier Zeilen in Abb. 3.3(a), die Einserbits produzieren, sind:  $\bar{A}\bar{B}C$ ,  $A\bar{B}C$ ,  $A\bar{B}\bar{C}$  und  $ABC$ . Die Funktion  $M$  ist wahr (d.h. 1), wenn eine dieser vier Bedingungen wahr ist. Folglich können wir

$$M = \bar{A}\bar{B}C + A\bar{B}C + A\bar{B}\bar{C} + ABC$$

als kompakte Wahrheitstabelle schreiben. Eine Funktion von  $n$  Variablen kann somit dadurch beschrieben werden, daß man einer »Summe« von höchstens  $2^n$   $n$ -Variablen »Produktterme« gibt. Wir werden gleich sehen, daß diese Form besonders wichtig ist, weil sie direkt zu einer Implementierung der Funktion unter Verwendung von Standard-Gates führt.

Wichtig ist die Unterscheidung zwischen einer abstrakten booleschen Funktion und ihrer Implementierung in einer elektronischen Schaltung. Eine boolesche Funktion besteht aus Variablen, z.B.  $A$ ,  $B$  und  $C$ , und booleschen Operatoren, z.B. AND, OR und NOT. Sie wird mit Hilfe einer Wahrheitstabelle oder einer booleschen Funktion, wie

$$F = \bar{A}\bar{B}C + A\bar{B}\bar{C}$$

beschrieben. Eine boolesche Funktion kann in einer elektronischen Schaltung (oft auf unterschiedliche Weise) mit Hilfe von Signalen implementiert werden, die die Ein- und Ausgangsvariablen und Gates, wie AND, OR und NOT, darstellen. Wir verwenden allgemein die Notation AND, OR und NOT in bezug auf boolesche Operatoren, und AND, OR und NOT in bezug auf Gates, was oft aber zweideutig ist.

### 3.1.3 Implementierung von booleschen Funktionen

Wie erwähnt, führt die Formulierung einer booleschen Funktion als Summe von bis zu  $2^n$  Produkttermen unmittelbar zu einer möglichen Implementierung. Anhand des Beispiels von Abb. 3.3 wird gezeigt, wie diese Implementierung erreicht wird. In Abb. 3.3(b) sind die Eingänge  $A$ ,  $B$  und  $C$  an der linken Kante und die Ausgangsfunktion  $M$  an der rechten Kante dargestellt. Da Komplemente (Umkehrfunktionen) der Eingangsvariablen erforderlich sind, werden sie durch Abgreifen der Eingänge (Tapping) erzeugt und durch die mit 1, 2 und 3 beschrifteten Inverter weitergegeben. Damit das Bild nicht unübersichtlich wird, haben wir sechs vertikale Linien gezeichnet, von denen drei mit den Eingangsvariablen und drei mit deren Komplementen verbunden sind. Diese Linien bieten eine bequeme Quelle für die Eingänge zu nachfolgenden Gates. Beispielsweise benutzen die Gates 5, 6 und 7 alle  $A$  als Eingang.

Bei einer echten Schaltung würde man diese Gates wahrscheinlich direkt, ohne dazwischenliegende »vertikale« Drähte, mit  $A$  verbinden.

Die Schaltung enthält vier AND-Gates, je eines für jeden Term in der Gleichung für  $M$  (d.h. eines für jede Zeile der Wahrheitstabelle, die in der Ergebnisspalte ein 1-Bit hat). Jedes AND-Gate berechnet eine Zeile der Wahrheitstabelle. Schließlich werden alle Produktterme mit OR verknüpft, um das Endergebnis zu ermitteln.

Die Schaltung von Abb. 3.3(b) basiert auf einer Konvention, die wir wiederholt in diesem Buch verwenden: Wenn sich zwei Linien kreuzen, ist dies keine Verbindung, es sei denn, auf dem Schnittpunkt befindet sich ein dicker Punkt. Der Ausgang von Gate 3 kreuzt z.B. alle sechs vertikalen Linien, ist aber nur mit  $\bar{C}$  verbunden. Man beachte, daß einige Autoren andere Konventionen verwenden.

Aus dem Beispiel von Abb. 3.3 wird deutlich, wie eine Schaltung für eine beliebige boolesche Funktion implementiert wird:

1. Schreibe die Wahrheitstabelle für die Funktion.

2. Erstelle Inverter, um das Komplement für jeden Eingang zu erzeugen.

3. Zeichne ein AND-Gate für jeden Term, mit einer 1 in der Ergebnisspalte.

4. Verdrahte die AND-Gates mit den entsprechenden Eingängen.

5. Speise den Ausgang aller AND-Gates in ein OR-Gate.

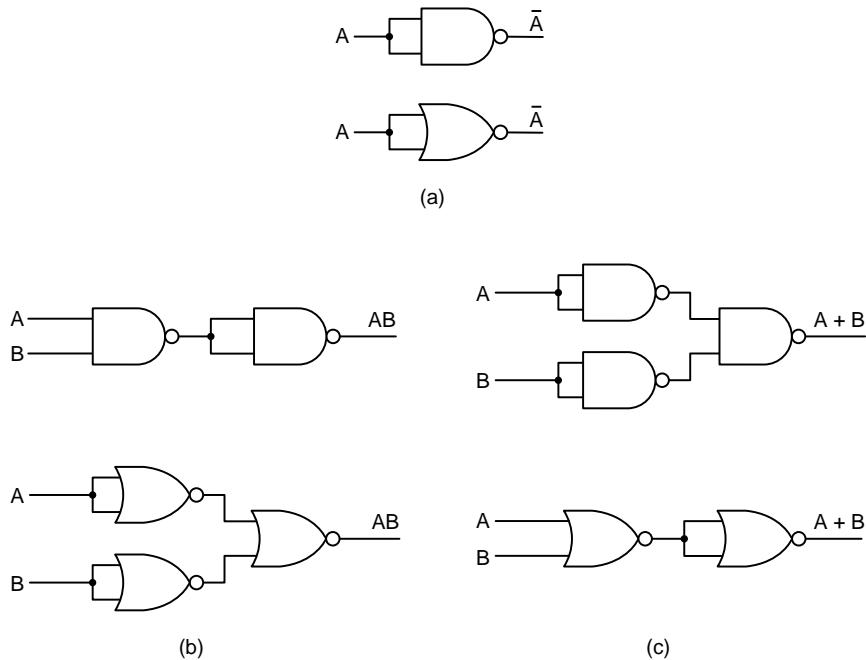

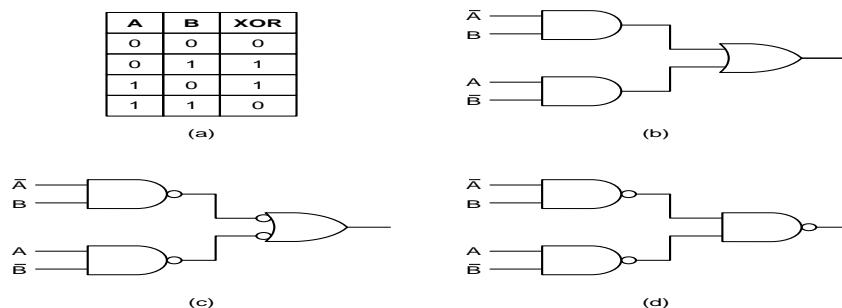

Damit haben wir aufgezeigt, wie eine boolesche Funktion mit Hilfe von NOT-, AND- und OR-Gates implementiert werden kann. Meist ist es aber praktischer, Schaltungen mit nur einer Sorte Gates zu implementieren. Zum Glück ist es nicht kompliziert, die mit dem obigen Algorithmus erzeugten Schaltungen in eine reine NAND- oder eine reine NOR-Form umzuwandeln. Für eine solche Umwandlung benötigen wir nur eine Möglichkeit, NOT, AND und OR mit Hilfe einer einzigen Gate-Art zu implementieren. Die oberste Zeile in Abb. 3.4 zeigt, wie alle drei Typen nur mit NAND-Gates implementiert werden können. Die unterste Zeile zeigt, wie dies nur mit NOR-Gates gelingt. (Das sind die einfachen, aber nicht die einzigen Möglichkeiten.)

Eine Möglichkeit, eine boolesche Funktion mit nur NAND- oder nur NOR-Gates zu implementieren, ist die Anwendung zuerst des oben beschriebenen Verfahrens, um sie mit NOT, AND und OR zu bilden. Dann ersetzt man die Gates mit mehreren Eingängen mit Hilfe von Gates mit zwei Eingängen durch gleichwertige Schaltungen. Benutzt man drei OR-Gates mit zwei Eingängen, kann  $A + B + C + D$  beispielsweise als  $(A + B) + (C + D)$  berechnet werden. Schließlich werden die NOT-, AND- und OR-Gates durch die Schaltungen von Abb. 3.4 ersetzt.

Im Sinne einer möglichst geringen Anzahl von Gates führt dieses Verfahren nicht zu optimalen Schaltungen, zeigt aber, daß es immer eine Lösung gibt. NAND- und NOR-Gates bezeichnet man als **komplett**, weil mit einem von bei-

den jede boolesche Funktion berechnet werden kann. Kein anderes Gate weist dieses Merkmal auf. Das ist ein weiterer Grund dafür, daß sie oft als Bausteine für Schaltungen benutzt werden.

### 3.1.4 Schaltungsäquivalenz

Entwickler von Schaltungen versuchen in der Regel, die Anzahl von Gates in ihren Produkten zu minimieren, um Komponentenkosten, PCB-Platz, Stromverbrauch usw. zu reduzieren. Zur Verringerung der Komplexität einer Schaltung muß der Entwickler eine andere Schaltung finden, die zwar die gleiche Funktion wie das Original berechnet, dies aber mit weniger Gates (oder auch einfacheren Gates, z.B. solchen mit zwei statt vier Eingängen) erreicht. Auf der Suche nach entsprechenden Schaltungen kann sich die boolesche Algebra als nützliches Werkzeug erweisen.

Abb. 3.4: Konstruktion von (a) NOT-, (b) AND- und (c) OR-Gates mit nur NAND- oder nur NOR-Gates

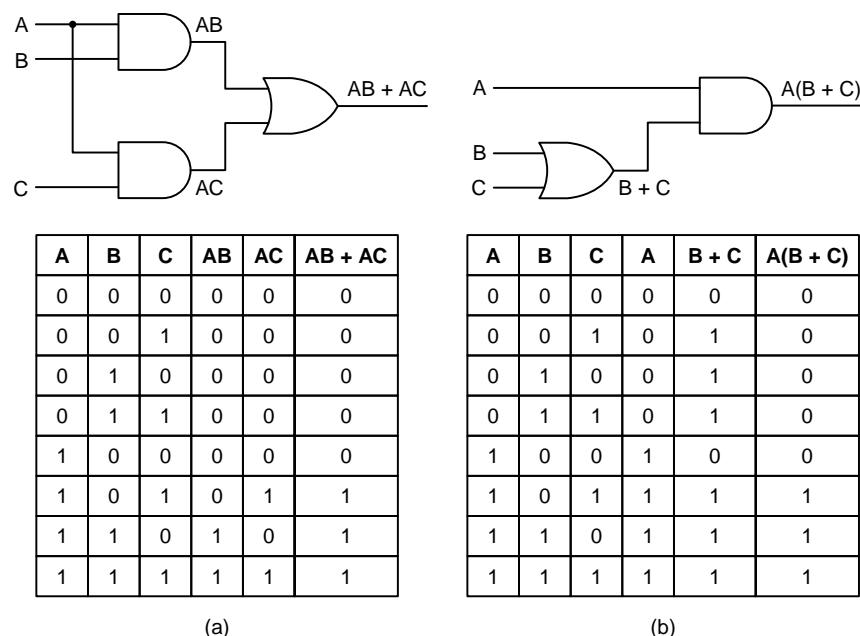

Als Beispiel dafür betrachte man die Schaltung und die Wahrheitstabelle für  $AB + AC$  in Abb. 3.5(a). Wir haben dies zwar noch nicht behandelt, viele Regeln der herkömmlichen Algebra treffen aber auch auf die boolesche zu. Insbesondere können  $AB + AC$  mit Hilfe des Distributivgesetzes in  $A(B + C)$  zusammengefaßt werden. Abb. 3.5(b) zeigt die Schaltung und die Wahrheitstabelle für  $A(B + C)$ . Da zwei Funktionen äquivalent sind, sofern sie den

gleichen und nur den gleichen Ausgang für alle möglichen Eingänge haben, wird aus den Wahrheitstabellen von Abb. 3.5 leicht ersichtlich, daß  $A(B + C)$  das Äquivalent zu  $AB + AC$  ist. Ungeachtet dessen ist die Schaltung von Abb. 3.5(b) deutlich besser als die in Abb. 3.5(a), weil sie weniger Gates enthält.

Im allgemeinen kann ein Schaltungsentwickler eine Schaltung als boolesche Funktion darstellen und dann die Gesetze der booleschen Algebra auf diese Darstellung anwenden, um eine einfachere und gleichwertige Schaltung zu finden. Aus der endgultigen Darstellung lsst sich eine neue Schaltung konstruieren.

Abb. 3.5: Zwei äquivalente Funktionen, (a)  $AB + AC$ , (b)  $A(B + C)$

Für diesen Ansatz benötigen wir einige Identitäten aus der booleschen Algebra. Abb. 3.6 zeigt einige der wichtigen. Interessant ist, daß jedes Gesetz zwei Formen hat, die gegenseitige **Duale** sind. Durch Austausch von AND und OR und auch von 0 und 1 kann eine Form aus der anderen produziert werden. Alle diese Gesetze können leicht durch Aufstellung entsprechender Wahrheitstabellen bewiesen werden. Mit Ausnahme der De Morganschen Gleichung, des Absorptionsgesetzes und der AND-Form des Distributivgesetzes sind die Ergebnisse mehr oder weniger selbsterklärend. Die De Morganschen Gleichungen können auf mehr als zwei Variablen erweitert werden, z.B.

$$\overline{ABC} = \overline{A} + \overline{B} + \overline{C}.$$

| Bezeichnung               | AND-Form                       | OR-Form                        |

|---------------------------|--------------------------------|--------------------------------|

| Identitätsgesetz          | $1A = A$                       | $0 + A = A$                    |

| Nullgesetz                | $0A = 0$                       | $1 + A = 1$                    |

| Idempotenzgesetz          | $AA = A$                       | $A + A = A$                    |

| Inversionsgesetz          | $A\bar{A} = 0$                 | $A + \bar{A} = 1$              |

| Kommutativgesetz          | $AB = BA$                      | $A + B = B + A$                |

| Assoziativgesetz          | $(AB)C = A(BC)$                | $(A + B) + C = A + (B + C)$    |

| Distributivgesetz         | $A + BC = (A + B)(A + C)$      | $A(B + C) = AB + AC$           |

| Absorptionsgesetz         | $A(A + B) = A$                 | $A + AB = A$                   |

| De Morgansche Gleichungen | $\bar{AB} = \bar{A} + \bar{B}$ | $\bar{A} + \bar{B} = \bar{AB}$ |

Abb. 3.6: Einige Identitäten der booleschen Algebra

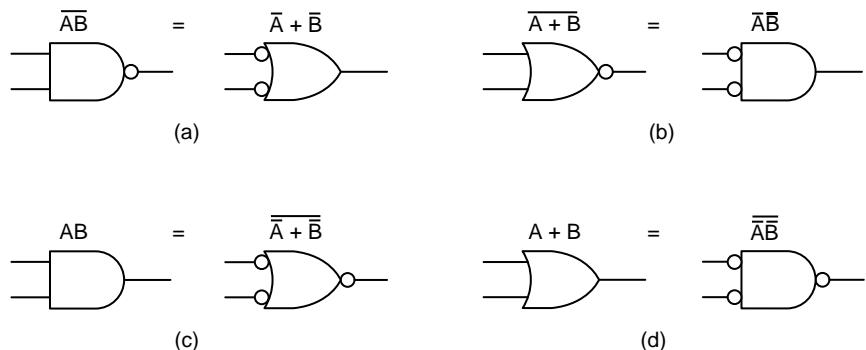

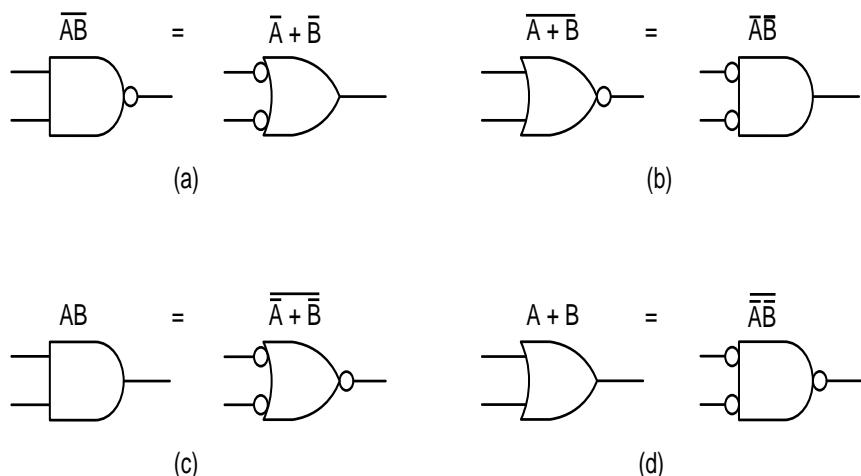

Die De Morganschen Gleichungen legen eine andere Schreibweise nahe. In Abb. 3.7(a) wird die AND-Form mit Negation, angedeutet durch Inversionsblasen, für Ein- und Ausgang dargestellt. Somit entspricht ein OR-Gate mit invertierten Eingängen einem NAND-Gate. Aus der dualen Form der De Morganschen Gleichungen in Abb. 3.7(b) wird deutlich, daß ein NOR-Gate als AND-Gate mit invertierten Eingängen gezeichnet werden kann. Durch Negation beider Formen der De Morganschen Gleichungen gelangen wir zu Abb. 3.7(c) und (d), den äquivalenten Darstellungen der AND- und OR-Gates. Entsprechende Symbole gibt es für mehrere variable Formen der De Morganschen Gleichungen (z.B. wird aus einem NAND-Gate mit  $n$  Eingängen ein OR-Gate mit  $n$  invertierten Eingängen).

Abb. 3.7: Alternative Symbole für einige Gates: (a) NAND, (b) NOR, (c) AND, (d) OR

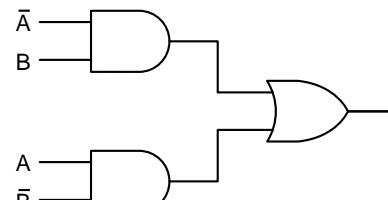

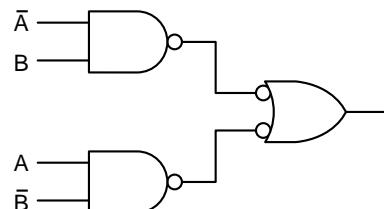

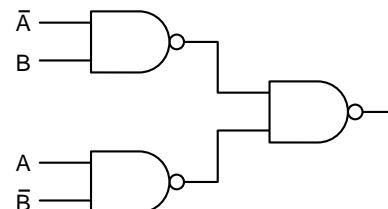

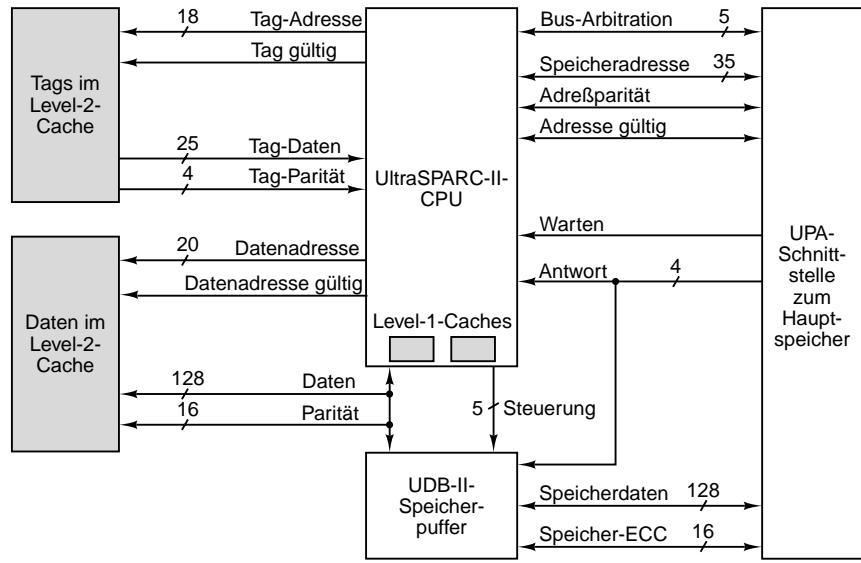

Mit Hilfe der Identitäten aus Abb. 3.7 und der entsprechenden für Gates mit mehreren Eingängen läßt sich die Produktsummandendarstellung einer Wahrheitstabelle leicht in die reine NAND- oder die reine NOR-Form umwandeln. Als Beispiel betrachte man die EXCLUSIVE-OR-Funktion von Abb. 3.8(a). Abb.

3.8(b) zeigt die Standardproduktsummenschaltung. Um in die NAND-Form umwandeln zu können, müssen die Linien, die den Ausgang der AND-Gates mit dem Eingang des OR-Gates verbinden, mit zwei Inversionsblasen neu gezeichnet werden wie in Abb. 3.8(c). Verwenden wir nun Abb. 3.7(a), gelangen wir zu Abb. 3.8(d). Die Variablen  $\bar{A}$  und  $\bar{B}$  können aus  $A$  und  $B$  erzeugt werden, wenn man NAND- oder NOR-Gates mit untereinander verbundenen Eingängen nimmt. Beachten Sie, daß Inversionsblasen entlang einer Linie beliebig verschoben werden können, beispielsweise von den Ausgängen der Eingangs-Gates in Abb. 3.8(d) zu den Eingängen des Ausgangs-Gates.

| A | B | XOR |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

(a)

(b)

(c)

(d)

Abb. 3.8: (a) Die Wahrheitstabelle für die EXCLUSIVE-OR-Funktion; (b)–(d) drei Schaltungen zu ihrer Berechnung

Abschließend zum Thema Schaltungsäquivalenz wird nun das überraschende Ergebnis aufgezeigt, daß das gleiche physische Gate verschiedene Funktionen je nach den benutzten Konventionen berechnen kann. In Abb. 3.9(a) zeigen wir den Ausgang eines bestimmten Gates  $F$  für verschiedene Eingangskombinationen. Eingänge und Ausgänge sind in Volt dargestellt. Einigen wir uns auf die Konvention, daß 0 Volt die logische 0 und 3,3 Volt oder 5 Volt die logische 1, **positive Logik** genannt, sind, dann erhalten wir die Wahrheitstabelle von Abb. 3.9(b), die AND-Funktion. Wenden wir demgegenüber die **negative Logik** an, bei der 0 Volt die logische 1 und 3,3 Volt oder 5 Volt die logische 0 sind, erhalten wir die Wahrheitstabelle von Abb. 3.9(c) bzw. die OR-Funktion.

Dies verdeutlicht, daß die zur Abbildung von Spannungen auf logische Werte gewählte Konvention von großer Bedeutung ist. Soweit nicht anders angegeben, verwenden wir ab jetzt die positive Logik, was bedeutet, daß die Begriffe »logische 1«, »wahr« und »High« sowie die Begriffe »logische 0«, »falsch« und »Low« Synonyme sind.

| A  | B  | F  |

|----|----|----|

| 0V | 0V | 0V |

| 0V | 5V | 0V |

| 5V | 0V | 0V |

| 5V | 5V | 5V |

| A | B | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| A | B | F |

|---|---|---|

| 1 | 1 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

Abb. 3.9: (a) Elektrische Merkmale eines Geräts; (b) positive Logik; (c) negative Logik

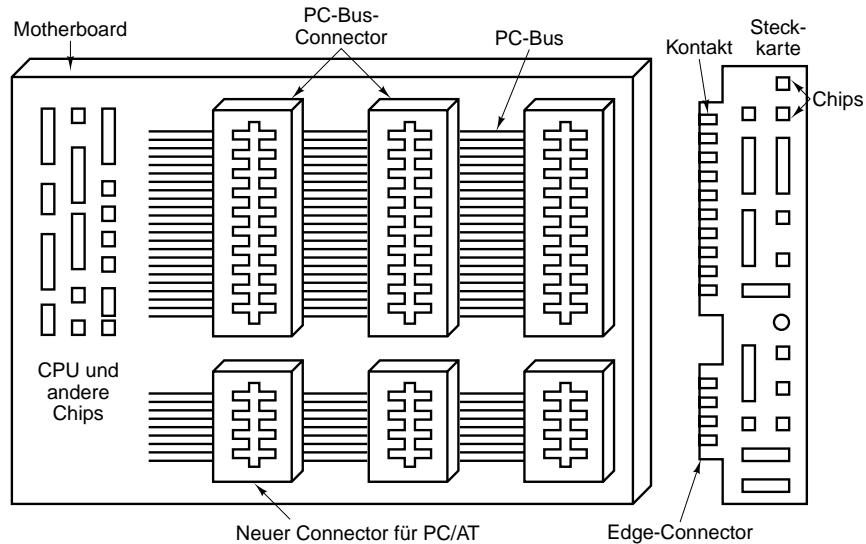

## 3.2 Grundlegende digitale logische Schaltungen

In den vorherigen Abschnitten haben wir gesehen, wie man Wahrheitstabellen und andere einfache Schaltungen mit einzelnen Gates implementieren kann. In der Praxis werden kaum noch Schaltungen auf einer Gate-zu-Gate-Basis entwickelt, obwohl dies früher die Regel war. Heute sind Module mit einer Reihe von Gates die gängigen Bausteine. In den folgenden Abschnitten betrachten wir diese Bausteine genauer. Es wird erklärt, wie sie benutzt werden und aus einzelnen Gates entwickelt werden können.

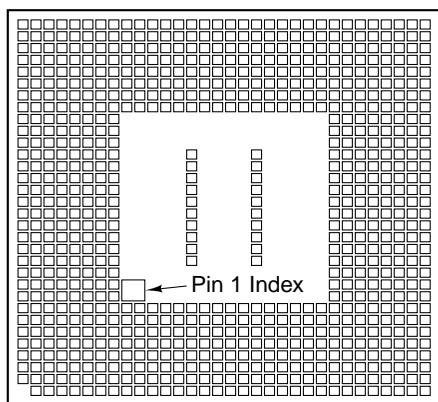

### 3.2.1 Integrierte Schaltungen

Gates werden nicht einzeln, sondern in Einheiten gefertigt und verkauft, die man **integrierte Schaltungen** oder **IC** (Integrated Circuits) oder **Chips** nennt. Ein IC ist ein quadratisches Stück Silikon in der Größe von etwa  $5 \times 5$  mm, das mit einigen Gates bestückt ist. Kleine ICs sind normalerweise auf einem rechteckigen Kunststoff- oder Keramikstück in der Abmessung 5 bis 15 mm breit und 20 bis 50 mm lang aufgebracht. An den langen Kanten befinden sich zwei parallele Reihen von Pins (Stiften), die etwa 5 mm lang sind, und die man in Stecker (Sockets) einstecken oder auf gedruckte Schaltkarten (Circuit Boards) aufschweißen kann. Jeder Pin paßt zum Ein- oder Ausgang eines Gates auf dem Chip oder zum Strom bzw. zur Masse. Die Einheiten mit zwei Pinreihen außen und IC innen tragen den technischen Fachausdruck **Dual Inline Packages** oder **DIP**. Jeder nennt sie aber Chips, so daß sich die Silikonstücke und die bestückten Einheiten von der Bezeichnung her nicht mehr unterscheiden. Die üblichen Einheiten haben 14, 16, 18, 20, 22, 24, 28, 40, 64 oder 68 Pins. Für größere Chips sind quadratische Einheiten mit Pins an allen vier Seiten oder an der Unterseite üblich.

Chips lassen sich nach der Anzahl von Gates, die sie aufweisen, in Klassen unterteilen. Diese Klassifizierung ist selbstverständlich sehr grob, dennoch aber nützlich:

- SSI-Schaltung (Small Scale Integrated): 1 bis 10 Gates

- MSI-Schaltung (Medium Scale Integrated): 10 bis 100 Gates

- LSI-Schaltung (Large Scale Integrated): 100 bis 100000 Gates

- VLSI-Schaltung (Very Large Scale Integrated): > 100000 Gates

Diese Klassen weisen unterschiedliche Merkmale auf und werden unterschiedlich benutzt.

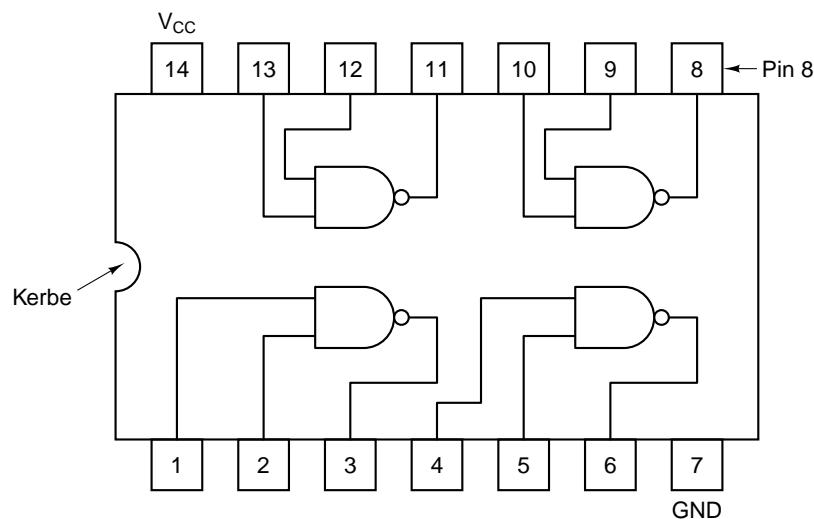

Ein SSI-Chip enthält normalerweise zwei bis sechs unabhängige Gates, die je einzeln wie in früheren Abschnitten beschrieben benutzt werden können. Abb. 3.10 zeigt einen üblichen SSI-Chip mit vier NAND-Gates. Jedes dieser Gates hat zwei Eingänge und einen Ausgang, so daß insgesamt 12 Pins für die vier Gates nötig sind. Außerdem braucht der Chip Strom ( $V_{cc}$ ) und Masse (GND), was beides von allen Gates benutzt wird. Die Einheit hat im allgemeinen nahe von Pin 1 eine Kerbe, die die Ausrichtung kennzeichnet. Um Schaltdiagramme nicht zu überladen, werden Strom, Masse und unbenutzte Gates normalerweise nicht dargestellt.

Abb. 3.10: SSI-Chip mit vier Gates

Für wenig Geld sind viele andere solcher Chips erhältlich. Jeder hat eine Handvoll Gates und bis zu 20 Pins. In den siebziger Jahren wurden Computer aus großen Mengen solcher Chips gebaut. Heute brennt man eine ganze CPU und einen großen Teil des (Cache) Speichers auf einen einzigen Chip.

Für unsere Zwecke sind alle Gates dahingehend ideal, daß der Ausgang erscheint, sobald der Eingang angewandt wird. In Wirklichkeit haben Chips eine endliche **Gate-Verzögerung** (Gate Delay), die sowohl die Signalausbreitung (Signal Propagation) durch den Chip als auch die Schaltzeit beinhaltet. Übliche Verzögerungen reichen von 1 bis 10 ns.

Nach dem derzeitigen Stand der Technik könnten fast 10 Millionen Transistoren auf einen einzigen Chip gepackt werden. Da jede Schaltung aus NAND-Gates gebaut werden kann, möchte man meinen, daß ein Hersteller einen sehr allgemeinen Chip mit 5 Millionen NAND-Gates fertigen kann. Leider würde ein solcher Chip 15.000.002 Pins benötigen. Bei einem Standardabstand von 0,1 Zoll zwischen den einzelnen Pins wäre der Chip über 18 km lang, was sich auf den Vertrieb des Chips doch sehr nachteilig auswirken würde. Die einzige Möglichkeit, die Technologie zu nutzen, ist also die Entwicklung von Schaltungen mit einem hohen Gate-Pin-Verhältnis. In den folgenden Abschnitten betrachten wir einfache MSI-Schaltungen, die intern eine Reihe von Gates auf sich vereinen, um eine nützliche Funktion zu bieten, wobei nur eine begrenzte Anzahl von externen Verbindungen (Pins) nötig ist.

### 3.2.2 Kombinationsschaltungen

Viele Anwendungen im Bereich der digitalen Logik erfordern eine Schaltung mit mehreren Ein- und Ausgängen, wobei die Ausgänge eindeutig durch die Stromeingänge bestimmt werden. Eine solche Schaltung nennt man **Kombinationsschaltung** (Combinational Circuit). Nicht alle Schaltungen weisen dieses Merkmal auf. Beispielsweise kann eine Schaltung, die Speicherelemente beinhaltet, Ausgänge erzeugen, die von den gespeicherten Werten und den Eingangsvariablen abhängen. Eine Schaltung, die eine Wahrheitstabelle implementiert, z.B. die von Abb. 3.3(a), ist ein typisches Beispiel einer Kombinationsschaltung. In diesem Abschnitt betrachten wir einige häufig benutzte Kombinationsschaltungen.

#### Multiplexer

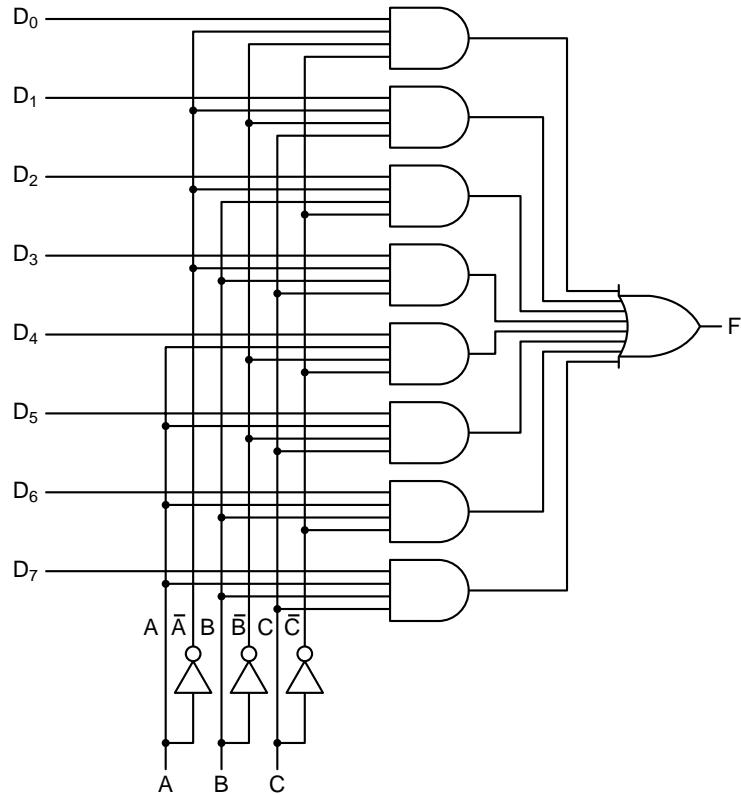

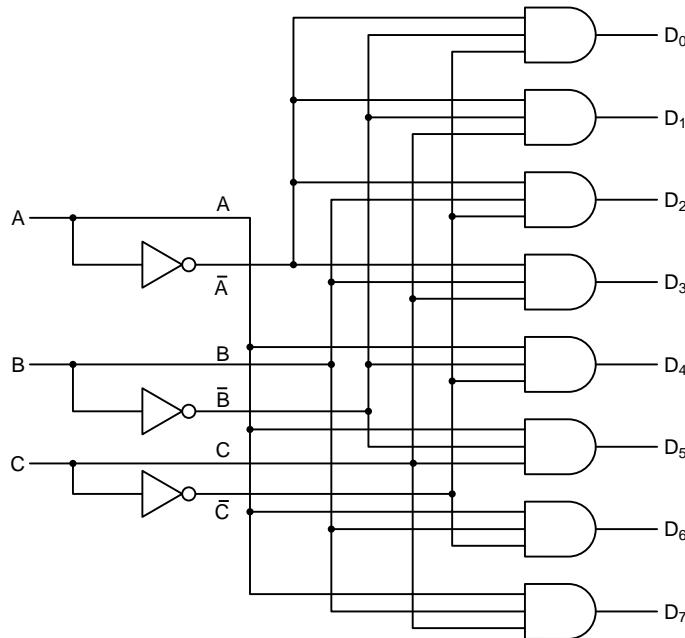

Auf der digitalen logischen Ebene ist ein **Multiplexer** eine Schaltung mit  $2^n$  Dateneingängen, einem Datenausgang und  $n$  Steuereingängen, die einen der Dateneingänge wählen. Der gewählte Dateneingang wird zum Ausgang geleitet. Abb. 3.11 zeigt schematisch einen Multiplexer mit acht Eingängen. Die drei Steuerleitungen  $A$ ,  $B$  und  $C$  kodieren eine 3-Bit-Zahl, die definiert, welche der acht Eingangsleitungen zum OR-Gate und somit zum Ausgang geleitet wird. Ungeachtet des Werts der Steuerleitungen sind sieben der AND-Gates immer Ausgang 0; das übrige kann je nach dem Wert der gewählten Eingangsleitung Ausgang 0 oder 1 sein. Jedes AND-Gate wird durch unterschiedliche Kombinationen der Steuereingänge aktiviert. Die Multiplexer-Schaltung ist aus Abb. 3.11 ersichtlich. Fügt man Strom und Masse hinzu, läßt sich das Teil auf eine 14-Pins-Einheit packen.

Abb. 3.11: Multiplexer-Schaltung mit acht Eingängen

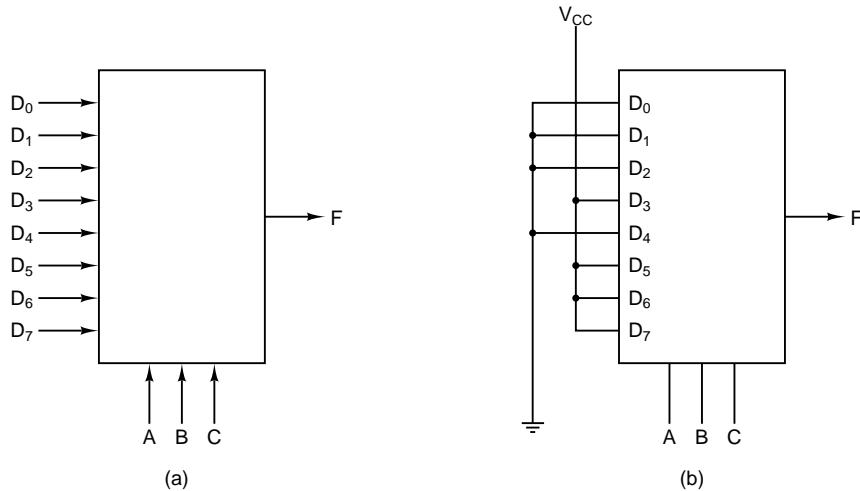

Mit Hilfe des Multiplexers können wir die Mehrheitsfunktion von Abb. 3.3(a) wie in Abb. 3.12(b) implementieren. Für jede Kombination von  $A$ ,  $B$  und  $C$  wird eine der Dateneingangsleitungen gewählt. Jeder Eingang wird entweder mit  $V_{cc}$  (logische 1) oder mit Masse (logische 0) verdrahtet. Der Algorithmus für die Verdrahtung der Eingänge ist einfach: Eingang  $D_i$  entspricht dem Wert in Zeile  $i$  der Wahrheitstabelle. In Abb. 3.3(a) sind die Zeilen 0, 1, 2 und 4 gleich 0, so daß die entsprechenden Eingänge geerdet sind. Die übrigen Zeilen sind 1, so daß sie mit der logischen 1 verbunden sind. Auf diese Weise kann eine beliebige Wahrheitstabelle von drei Variablen mit dem Chip von Abb. 3.12(a) implementiert werden.

Abb. 3.12: (a) MSI-Multiplexer-Chip; (b) der gleiche Chip zur Berechnung der Mehrheitsfunktion verschaltet

Wir haben bereits gesehen, wie ein Multiplexer-Chip benutzt werden kann, um einen von mehreren Eingängen zu wählen, und wie er eine Wahrheitstabelle implementieren kann. Als weiterer Anwendungsbereich ist ein Parallel/Seriell-Datenwandler machbar. Legt man 8 Datenbits auf die Eingangsleitungen und schaltet man die Steuerleitungen sequentiell von 000 bis 111 (binär) weiter, werden diese in Reihe auf die Ausgangsleitung gelegt. Eine typische Nutzung für die Parallel/Seriell-Umwandlung ist eine Tastatur. Dabei definiert jeder Anschlag implizit eine 7- oder 8-Bit-Zahl, die seriell über eine Telefonleitung ausgegeben werden muß.

Das Gegenstück eines Multiplexers ist ein **Demultiplexer**, der je nach den Werten der  $n$  Steuerleitungen ein einzelnes Eingangssignal auf einen von  $2^n$  Ausgängen leitet. Beträgt der Binärwert auf den Steuerleitungen  $k$ , wird Ausgang  $k$  gewählt.

### Dekodierer

Als zweites Beispiel eines MSI-Chips betrachten wir eine Schaltung, die eine  $n$ -Bit-Zahl als Eingabe annimmt und sie benutzt, um genau eine der  $2^n$  Ausgangsleitungen zu wählen (d.h. auf 1 zu setzen). Eine solche Schaltung nennt man **Dekodierer** (Decoder). Abb. 3.13 zeigt ein Beispiel mit  $n = 3$ .

Abb. 3.13: 3-zu-8-Dekodierer-Schaltung

Um den Nutzen eines Dekodierers zu sehen, stelle man sich einen Speicher vor, der aus acht Chips mit je 1 Mbyte besteht. Chip 0 hat die Adressen 0 bis 1 Mbyte, Chip 1 die Adressen 1 Mbyte bis 2 Mbyte usw. Wird eine Adresse im Speicher dargestellt, werden die 3 höherwertigen Bits benutzt, um einen der acht Chips zu wählen. Unter Verwendung der Schaltung von Abb. 3.13 sind diese 3 Bits die drei Eingänge  $A$ ,  $B$  und  $C$ . Je nach den Eingängen ist genau eine der acht Ausgangsleitungen  $D_0, \dots, D_7$  gleich 1, und die restlichen sind 0. Jede Ausgangsleitung aktiviert einen der acht Speicherchips. Da nur eine Ausgangsleitung auf 1 gesetzt wurde, ist nur ein Chip eingeschaltet.

Die Betriebsweise der Schaltung von Abb. 3.13 ist leicht nachvollziehbar. Jedes AND-Gate hat drei Eingänge, von denen der erste entweder  $A$  oder  $\bar{A}$ , der zweite entweder  $B$  oder  $\bar{B}$  und der dritte entweder  $C$  oder  $\bar{C}$  ist. Jedes Gate wird durch eine andere Eingangskombination eingeschaltet:  $D_0$  durch  $ABC$ ,  $D_1$  durch  $\bar{A}\bar{B}C$  usw.

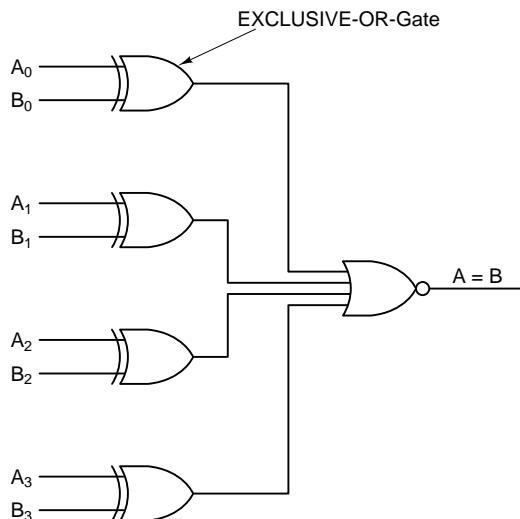

### Komparatoren

Eine weitere nützliche Schaltung ist der **Komparator** (Comparator), der zwei Eingangswörter vergleicht. Der einfache Komparator von Abb. 3.14 nimmt zwei Eingaben  $A$  und  $B$  mit einer Länge von je 4 Bits und produziert 1, falls sie gleich sind, und 0, falls sie ungleich sind. Die Schaltung basiert auf dem EXCLUSIVE-OR-Gate (XOR), das eine 0 ausgibt, wenn seine Eingänge gleich sind, und eine 1 ausgibt, wenn sie ungleich sind. Sind die beiden Eingabewör-

ter gleich, müssen alle vier XOR-Gates 0 ausgeben. Diese vier Signale können dann mit OR verknüpft werden. Ist das Ergebnis 0, sind die Eingabewörter gleich, andernfalls nicht. In unserem Beispiel haben wir ein NOR-Gate als endgültiges Stadium zur Umkehrung der Prüfrichtung benutzt: 1 bedeutet gleich und 0 bedeutet ungleich.

Abb. 3.14: Einfacher 4-Bit-Komparator

### Programmierte Logik-Arrays

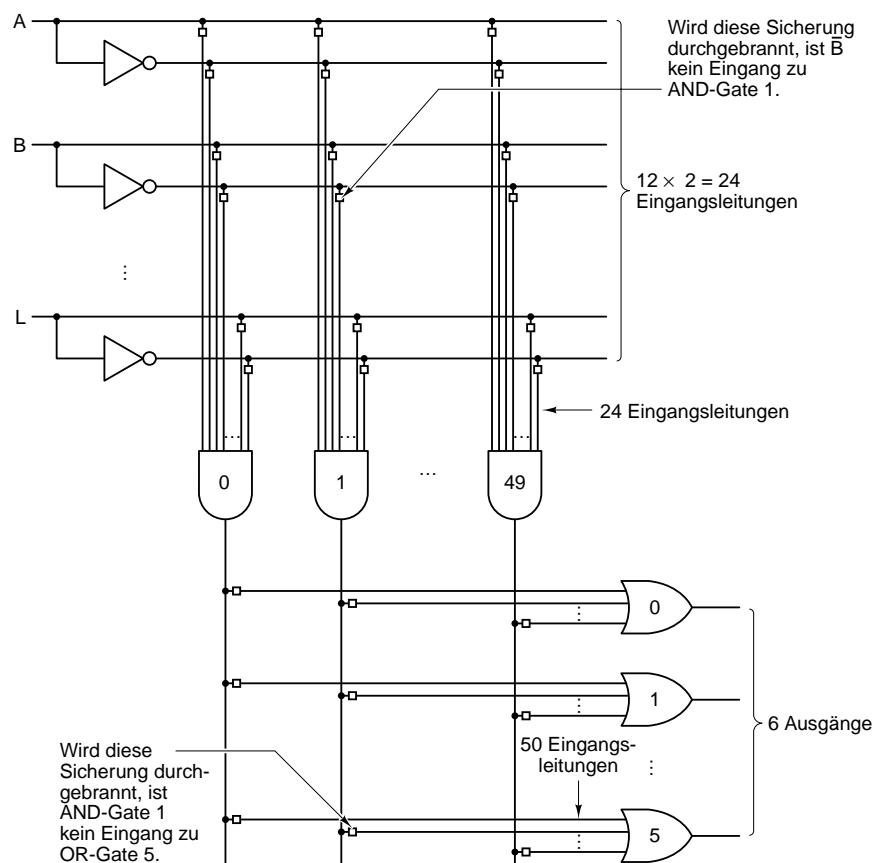

Wir haben bereits gesehen, daß beliebige Funktionen (Wahrheitstabellen) dadurch erzeugt werden können, daß man Produktterme mit AND-Gates berechnet und dann die Produkte mit OR verknüpft. Ein sehr allgemeiner Chip zur Summenbildung von Produkten ist das **programmierbare Logik-Array** (Programmable Logic Array – PLA). Abb. 3.15 zeigt ein einfaches Beispiel. Dieser Chip hat Eingangsleitungen für 12 Variablen. Das Komplement jedes Eingangs wird intern erzeugt, so daß sich insgesamt 24 Eingangssignale ergeben. Der Kern der Schaltung ist ein Array von 50 AND-Gates, die jeweils potentiell jede beliebige Untergruppe von 24 Eingangssignalen als Eingabe haben können. Welches Eingangssignal an welches AND-Gate geht, wird durch eine  $24 \times 50$ -Bit-Matrix bestimmt, die vom Benutzer bereitgestellt wird. Jede Eingangsleitung zu den 50 AND-Gates enthält eine Sicherung. Bei Auslieferung sind alle 1200 Sicherungen intakt. Um die Matrix zu programmieren, brennt der Benutzer durch Anlegen einer hohen Spannung auf den Chip ausgewählte Sicherungen durch.

Der Ausgangsteil der Schaltung besteht aus sechs OR-Gates, die entsprechend den 50 Ausgängen der AND-Gates je bis zu 50 Eingänge haben. Auch hier bestimmt die vom Benutzer bereitgestellte ( $50 \times 6$ ) Matrix, welche der potentiell

len Verbindungen tatsächlich existiert. Der Chip hat 12 Eingangspins, 6 Ausgangspins sowie Strom und Masse, d.h. insgesamt 20 Pins.

Als praktisches Beispiel eines PLAs ziehen wir wieder die Schaltung von Abb. 3.3(b) heran. Sie hat drei Eingänge, vier AND-Gates, ein OR-Gate und drei Inverter. Mit den entsprechenden internen Verbindungen kann unser PLA diese Funktion mit Hilfe seiner 12 Eingänge, vier seiner 50 AND-Gates und einem seiner sechs OR-Gates berechnen. (Die vier AND-Gates sollten  $\bar{A}B\bar{C}$ ,  $A\bar{B}\bar{C}$ ,  $A\bar{B}C$  bzw.  $ABC$  berechnen. Das OR-Gate nimmt diese vier Produktterme als Eingabe an.) Wir könnten den gleichen PLA so verdrahten, daß er gleichzeitig insgesamt vier Funktionen ähnlicher Komplexität berechnet. Für diese einfachen Funktionen ist der Begrenzungsfaktor die Anzahl der EingabevARIABLEN; für komplexere könnten es die AND- oder OR-GATES sein.

Abb. 3.15: Programmierbares Logik-Array (PLA) mit 12 Ein- und 6 Ausgängen. Die kleinen Quadrate stellen Sicherungen dar, die zur Bestimmung der zu berechnenden Funktion ausgebrannt werden können. Die Sicherungen sind in zwei Matrizen angeordnet: die obere für die AND-Gates und die untere für die OR-Gates.

Obwohl solche im Feld programmierbare PLAs noch in Gebrauch sind, werden individuell angepaßte PLAs für viele Anwendungen bevorzugt. Diese Einheiten werden vom Großabnehmer entwickelt und vom Hersteller gemäß den Kundenspezifikationen gefertigt. Sie sind billiger als die im Feld programmierbaren.

Wir können jetzt die drei verschiedenen Implementierungsmöglichkeiten der Wahrheitstabelle von Abb. 3.3(a) vergleichend gegenüberstellen. Bei SSI-Komponenten brauchen wir vier Chips. Alternativ würde ein MSI-Multiplexer-Chip (Abb. 3.12(b)) ausreichen. Schließlich könnten wir ein Viertel eines PLA-Chips benutzen. Werden viele Funktionen benötigt, ist der PLA natürlich effizienter als die anderen beiden Methoden. Für einfache Schaltungen sind die billigeren SSI- und MSI-Chips sicherlich vorzuziehen.

### 3.2.3 Arithmetische Schaltungen

Jetzt ist es an der Zeit, uns von den oben behandelten MSI-Allzweckschaltungen auf MSI-Kombinationsschaltungen zu verlagern, die für arithmetische Berechnungen benutzt werden. Wir beginnen mit einem einfachen 8-Bit-Schieber; dann betrachten wir einen Addierer und schließlich arithmetische Logikeinheiten, die in jedem Computer eine zentrale Rolle spielen.

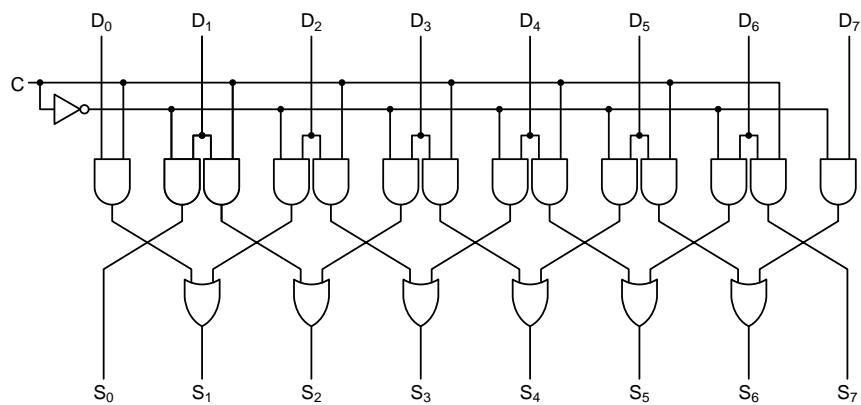

#### Schieber

Unsere erste arithmetische MSI-Schaltung ist ein **Schieber** (Shifter) mit acht Eingängen und acht Ausgängen (siehe Abb. 3.16). Acht Eingangsbits sind auf den Leitungen  $D_0, \dots, D_7$  dargestellt. Der Ausgang, der lediglich der um ein Bit verschobene Eingang ist, ist auf den Leitungen  $S_0, \dots, S_7$  verfügbar. Die Steuerleitung  $C$  bestimmt die Richtung der Verschiebung; sie beträgt 0 = links und 1 = rechts.

Abb. 3.16: 1-Bit-Schieber links/rechts

Um die Funktionsweise der Schaltung zu sehen, beachte man die Paare von AND-Gates für alle Bits, mit Ausnahme der Gates am Ende. Wenn  $C = 1$ , wird das rechte Mitglied jedes Paars eingeschaltet, wodurch das entsprechende Eingangsbit zum Ausgang gereicht wird. Da das rechte AND-Gate mit dem Eingang des OR-Gates rechts daneben verdrahtet ist, wird eine Verschiebung nach rechts durchgeführt. Wenn  $C = 0$ , wird das linke Mitglied des AND-Gates eingeschaltet, wodurch sich eine Verschiebung nach links ergibt.

### Addierer

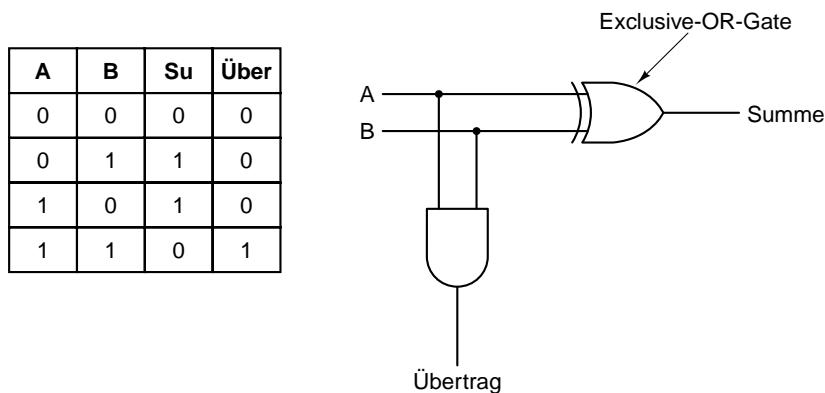

Ein Computer, der keine Ganzzahlen addieren kann, ist undenkbar. Folglich sind Schaltungen zur Durchführung von Additionen ein unentbehrlicher Teil jeder CPU. Die Wahrheitstabelle für eine 1-Bit-Addition ist in Abb. 3.17(a) dargestellt. Hier gibt es zwei Ausgänge, die Summe der Eingänge  $A$  und  $B$  und den Übertrag zur nächsten Stelle (nach links). Abb. 3.17(b) zeigt eine Schaltung zur Berechnung von Summe und Übertrag. Diese Schaltung heißt **Halbaddierer** (Half Adder).

Abb. 3.17: (a) Wahrheitstabelle für eine 1-Bit-Addition; (b) Schaltung für einen Halbaddierer

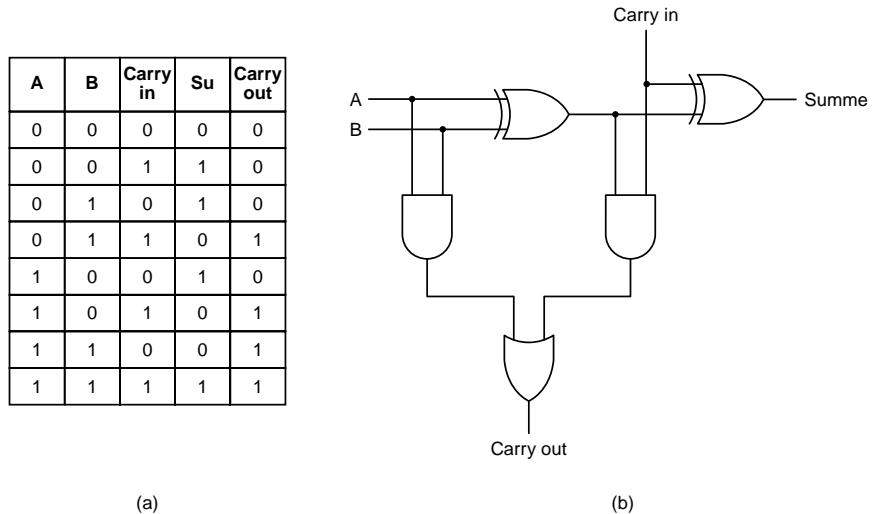

Nun ist ein Halbaddierer zwar für die Addition der niederwertigen Bits zweier aus mehreren Bits bestehenden Eingabewörter geeignet, reicht aber nicht für eine Bitstelle in der Wortmitte, weil er den Übertrag an die Stelle von rechts nicht durchführt. Hier benötigt man den **Volladdierer** (Full Adder) von Abb. 3.18. Aus Sicht der Schaltung ist klar, daß ein Volladdierer aus zwei Halbaddierern besteht. Die Ausgangsleitung *Sum* ist 1, wenn eine ungerade Zahl von  $A$ ,  $B$  und *Carry in* 1 sind. *Carry out* ist 1, wenn entweder  $A$  und  $B$  beide 1 sind (linker Eingang zum OR-Gate) oder eine davon 1 und das *Carry-in*-Bit ebenfalls 1 ist. Zusammen erzeugen die beiden Halbaddierer sowohl die Summen- als auch die Übertragsbits.

Abb. 3.18: (a) Wahrheitstabelle und (b) Schaltung für einen Volladdierer

Um einen Addierer für, sagen wir, zwei 16-Bit-Wörter zu bauen, wiederholt man lediglich die Schaltung von Abb. 3.18(b) 16 Mal. Das *Carry out* eines Bits braucht man als Übertrag in die linke Nachbarstelle. Der Übertrag in das Bit ganz rechts wird auf 0 verdrahtet. Dies nennt man **Ripple Carry Adder** (in etwa: Durchlaufübertragaddierer bzw. Addierer mit Übertragsweiterleitung), weil die Addition von 1 zu 111...111 (binär) im schlechtesten Fall so lange nicht beendet werden kann, bis der Übertrag die ganze Strecke vom ganz linken zum ganz rechten Bit durchlaufen hat. Es gibt auch Addierer, die diese Verzögerung nicht haben und somit schneller sind.

Als einfaches Beispiel eines schnelleren Addierers teilen wir einen 32-Bit-Addierer in eine untere Hälfte und eine obere Hälfte von je 16 Bits auf. Bei Beginn der Addition kann sich der obere Addierer noch nicht an die Arbeit machen, weil er noch nicht weiß, welchen Übertrag er für die 16 Additionen übernehmen muß.

Sehen Sie sich aber diese Veränderung an: Statt einer einzelnen oberen Hälfte verleihen wir dem Addierer durch Duplizierung der Hardware der oberen Hälfte parallel zwei obere Hälften. Jetzt besteht die Schaltung aus drei 16-Bit-Addierern: einer unteren Hälfte und zwei oberen Hälften  $U_0$  und  $U_1$ , die parallel laufen. Eine 0 wird als Übertrag in  $U_0$  gespeist; eine 1 wird als Übertrag in  $U_1$  gespeist. Jetzt können diese beiden gleichzeitig mit der unteren Hälfte starten, aber nur einer wird korrekt sein. Nach 16 Bitadditionen wird der in die obere Hälfte zu übernehmende Übertrag bekannt sein, so daß die richtige obere Hälfte nun aus den beiden verfügbaren Optionen ausgewählt werden kann. Auf diese Weise wird die Additionshäufigkeit um einen Faktor von Zwei verringert. Einen solchen Addierer nennt man **Carry Select Adder** (in etwa:

Übertragsauswahladdierer). Dieser Trick lässt sich wiederholen, um jeden 16-Bit-Addierer aus replizierten 8-Bit-Addierern usw. zu konstruieren.

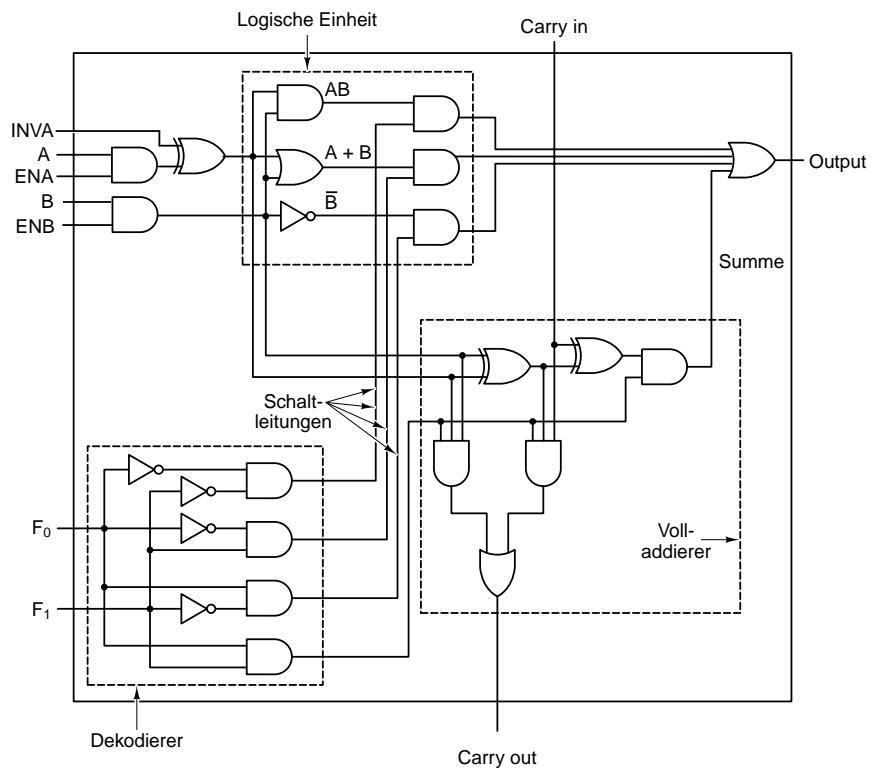

### Arithmetische Logikeinheiten

Die meisten Computer enthalten zur Durchführung von AND, OR und Addition zweier Maschinenwörter nur eine Schaltung. Normalerweise wird eine solche Schaltung für  $n$ -Bit-Wörter aus  $n$  identischen Schaltungen für die einzelnen Bitstellen gebaut. Abb. 3.19 ist ein einfaches Beispiel einer solchen Schaltung, die man **arithmetische Logikeinheit** (Arithmetic Logic Unit – ALU) nennt. Sie kann vier Funktionen, nämlich  $A \text{ AND } B$ ,  $A \text{ OR } B$ ,  $\bar{B}$  oder  $A + B$  berechnen, je nachdem, ob  $F_0$  und  $F_1$  die für die Funktionen gewählten Eingangsleitungen 00, 01, 10 oder 11 (binär) enthalten. Hier bedeutet  $A + B$  die arithmetische Summe von  $A$  und  $B$ , und nicht das boolesche AND.

Abb. 3.19: Eine 1-Bit-ALU

In der unteren linken Ecke unserer ALU befindet sich ein 2-Bit-Dekodierer, der die Schaltsignale für die vier Operationen auf der Grundlage von  $F_0$  und  $F_1$  erzeugt. Je nach den Werten von  $F_0$  und  $F_1$  wird genau eine der vier Schaltelemente gewählt. Die Assertion dieser Leitung erlaubt dem Ausgang der ge-

wählten Funktion, bezüglich des Ausgangs bis zum letzten OR-Gate zu passieren.

In der oberen linken Ecke befindet sich die Logik zur Berechnung von  $A \text{ AND } B$ ,  $A \text{ OR } B$  und  $\bar{B}$ ; höchstens eines dieser Ergebnisse wird aber an das letzte OR-Gate weitergereicht, je nach den aus dem Dekodierer austretenden Schalteitungen. Da genau einer der Dekodierer-Ausgänge 1 ist, wird genau eines der vier das OR-Gate steuernden AND-Gates eingeschaltet; die übrigen drei sind Ausgang 0, unabhängig von  $A$  und  $B$ .

Abgesehen davon, daß man  $A$  und  $B$  als Eingänge für logische oder arithmetische Operationen benutzen kann, ist es auch möglich, einen davon auf 0 zu zwingen, wenn man ENA bzw. ENB negiert. Außerdem erhält man  $\bar{A}$  durch Assertion von INVA. Anwendungen für INVA, ENA und ENB werden in Kapitel 4 behandelt. Unter normalen Bedingungen werden ENA und ENB asseriert, um beide Eingänge einzuschalten, und INVA wird negiert. In diesem Fall werden  $A$  und  $B$  einfach unverändert in die Logikeinheit eingespeist.

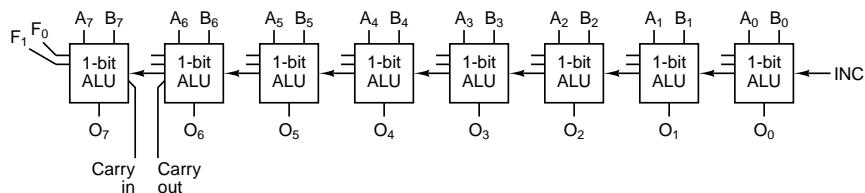

In der unteren rechten Ecke der ALU befindet sich ein Volladdierer zur Berechnung der Summe von  $A$  und  $B$ , einschließlich den Überträgen, weil wahrscheinlich mehrere dieser Schaltungen letztendlich parallel verschaltet werden, um Vollwort-Operationen durchzuführen. Chips wie der in Abb. 3.19 sind im Handel erhältlich und werden als **Bit-Slice-Prozessoren** (Bitscheiben-Prozessoren) bezeichnet. Sie ermöglichen es dem Computer-Designer, eine ALU in jeder gewünschten Breite zu entwerfen. Abb. 3.20 zeigt eine 8-Bit-ALU, die sich aus acht 1-Bit-ALU-Slices zusammensetzt. Das INC-Signal ist nur für Additionen nützlich. Bei Assertion erhöht es das Ergebnis um 1, so daß es möglich ist, Summen wie  $A + 1$  und  $A + B + 1$  zu berechnen.

Abb. 3.20: Acht 1-Bit-ALU-Slices sind verbunden und bilden eine 8-Bit-ALU

### 3.2.4 Taktgeber

In vielen digitalen Schaltungen ist die Reihenfolge, in der Ereignisse passieren, von maßgeblicher Bedeutung. Zuweilen muß ein Ereignis einem anderen vorausgehen, in anderen Fällen müssen zwei Ereignisse gleichzeitig eintreten. Damit Entwickler die erforderlichen Zeitrelationen erreichen können, sind viele digitale Schaltungen mit Taktgebern zum Zwecke der Synchronisation ausgestattet. Ein **Taktgeber** (Clock) ist in diesem Zusammenhang eine Schaltung, die eine Reihe von Impulsen in einer präzisen Impulsbreite und in ei-

nem präzisen Intervall zwischen aufeinanderfolgenden Impulsen ausgibt. Das Intervall zwischen entsprechenden Kanten von zwei aufeinanderfolgenden Impulsen nennt man **Taktzykluszeit** (Clock Cycle Time). Impulsfrequenzen liegen normalerweise zwischen 1 MHz und 500 MHz und entsprechen den Taktzyklen von 1000 ns bis 2 ns. Zur Erzielung einer hohen Genauigkeit wird die Taktfrequenz normalerweise von einem Kristalloszillatator gesteuert.

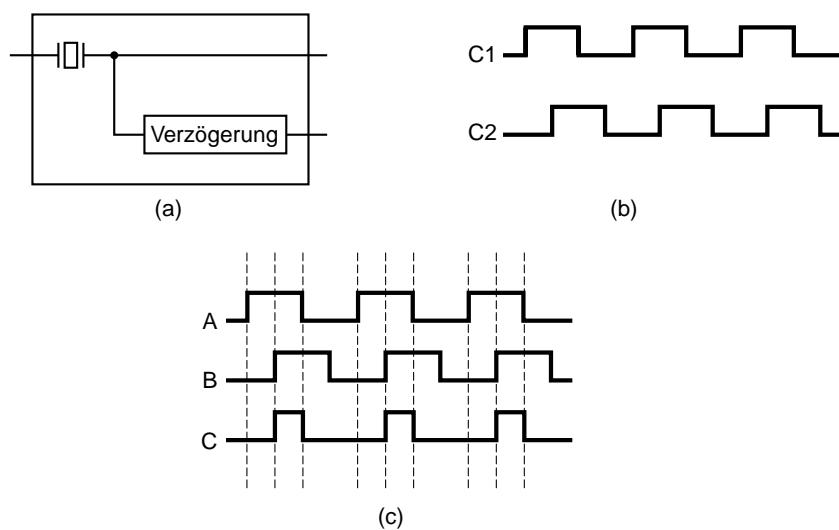

In einem Computer können innerhalb eines einzigen Taktzyklus viele Ereignisse ablaufen. Sollen diese Ereignisse in einer bestimmten Reihenfolge eintreten, muß der Taktzyklus in Teilzyklen aufgeteilt werden. Ein übliches Vorgehen, eine feinere Auflösung als der einfache Taktgeber zu bieten, ist die Anzapfung der primären Taktleitung und das Einfügen einer Schaltung mit einer bekannten Verzögerung, so daß ein sekundäres, zum primären phasenverschobenes Taktsignal erzeugt wird (siehe Abb. 3.21(a)). Das Taktdiagramm von Abb. 3.21(b) bietet vier Taktverweise für bestimmte Ereignisse:

1. Steigende Flanke von C1

2. Fallende Flanke von C1

3. Steigende Flanke von C2

4. Fallende Flanke von C2

Verknüpft man verschiedene Ereignisse mit den verschiedenen Flanken, läßt sich die erforderliche Abfolge umsetzen. Werden innerhalb eines Taktzyklus mehr als vier Zeitverweise benötigt, kann man mehr sekundäre Leitungen von der primären aus anzapfen und mit verschiedenen Verzögerungen belegen.

Abb. 3.21: (a) Taktgeber; (b) Taktdiagramm für den Taktgeber; (c) Erzeugung eines asymmetrischen Taks

Bei manchen Schaltungen ist man mehr an Zeitintervallen als an diskreten Zeitinstanzen interessiert. Ein Ereignis kann z.B. jederzeit eintreten, wenn C1 auf High und nicht genau an der steigenden Flanke liegt. Ein weiteres Ereignis kann nur eintreten, wenn C2 auf High liegt. Werden mehr als zwei Intervalle benötigt, stellt man mehrere Taktleitungen bereit oder die High-Zustände der beiden Taktgeber so ein, daß sie zeitlich teilweise überlappen. Im letzteren Fall lassen sich vier Intervalle unterscheiden:  $\overline{C1} \text{ AND } \overline{C2}$ ,  $\overline{C1} \text{ AND } C2$ ,  $C1 \text{ AND } \overline{C2}$  und  $C1 \text{ AND } C2$ .

Nebenbei bemerkt sind Taktgeber symmetrisch, wobei die im High-Zustand ablaufende Zeit der Zeit entspricht, die im Low-Zustand abläuft, wie aus Abb. 3.21(b) ersichtlich ist. Um eine asymmetrische Impulsfolge zu erzeugen, wird der Basistakt mit Hilfe einer Verzögerungsschaltung verschoben und mittels AND mit dem Ursprungssignal verknüpft, wie C in Abb. 3.21(c).

### 3.3 Speicher

Eine wesentliche Komponente eines jeden Computers ist sein Speicher. Ohne Speicher wären Computer nicht das, was sie sind. Ein Speicher dient der Speicherung auszuführender Instruktionen und Daten. In den folgenden Abschnitten werden die grundlegenden Komponenten eines Speichersystems, mit der Gate-Ebene beginnend, behandelt, um aufzuzeigen, wie sie funktionieren und zu großen Speichern zusammengefaßt werden können.

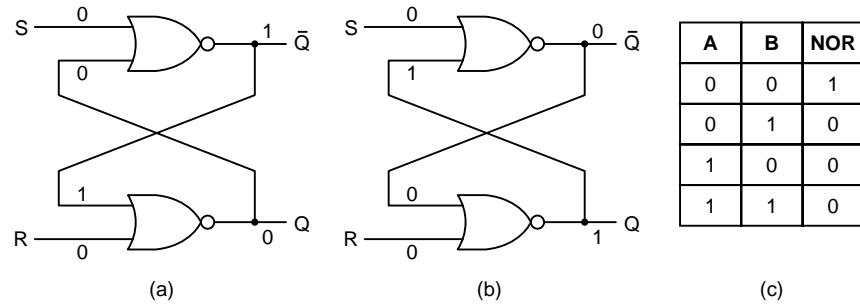

#### 3.3.1 Latches

Um einen 1-Bit-Speicher zu erstellen, brauchen wir eine Schaltung, die sich irgendwie vorherige Eingabewerte »merkt«. Eine solche Schaltung lässt sich aus zwei NOR-Gates bauen (siehe Abb. 3.22(a)). Analoge Schaltungen können aus NAND-Gates gebaut werden. Wir erwähnen diese nicht weiter, weil sie vom Konzept her mit den NOR-Versionen identisch sind.

Abb. 3.22: (a) NOR-Latch im Zustand 0; (b) NOR-Latch im Zustand 1; (c) Wahrheitstabelle für NOR

Die Schaltung von Abb. 3.22(a) nennt man **SR-Latch**. Sie hat zwei Eingänge –  $S$  zum Setzen der Latch und  $R$  zum Zurücksetzen (d.h. Löschen) derselben. Ferner hat sie zwei komplementäre Ausgänge  $Q$  und  $\bar{Q}$ , wie wir gleich sehen werden. Im Gegensatz zu einer Kombinationsschaltung werden die Ausgänge der Latch nicht eindeutig durch die Stromeingänge bestimmt.

Das hat folgenden Grund: Angenommen,  $S$  und  $R$  sind 0, was sie die meiste Zeit sind. Weiter nehmen wir an, daß  $Q = 0$ . Da  $Q$  in das obere NOR-Gate zurückgespeist wird, sind seine beiden Eingänge 0; deshalb ist sein Ausgang  $\bar{Q} = 1$ . Die 1 wird in das untere Gate zurückgespeist, das dann die Eingänge 1 und 0 hat, woraus sich  $Q = 0$  ergibt. Dieser Zustand ist konsistent und aus Abb. 3.22(a) ersichtlich.

Nun stellen wir uns vor, daß  $Q$  nicht 0, sondern 1 ist, während  $R$  und  $S$  immer noch 0 sind. Das obere Gate hat die Eingänge 0 und 1 und einen Ausgang  $\bar{Q}$  von 0, der zum unteren Gate zurückgespeist wird. Dieser Zustand (siehe Abb. 3.22(b)) ist ebenfalls konsistent. Ein Zustand, bei dem beide Ausgänge gleich 0 sind, ist konsistent, weil er beide Gates zu zwei Nullen als Eingang zwingt, was im Falle von wahr 1 und nicht 0 als Ausgang produzieren würde. Ebenso ist es möglich, daß beide Ausgänge gleich 1 sind, weil dies die Eingänge auf 0 und 1 zwingen würde, was 0 und nicht 1 ergibt. Unsere Schlußfolgerung ist einfach: Bei  $R = S = 0$  hat die Latch zwei stabile Zustände, die wir abhängig von  $Q = 0$  und  $1$  nennen.

Jetzt prüfen wir die Wirkung der Eingänge auf den Zustand der Latch. Angenommen,  $S$  wird 1, während  $R = 0$ . Die Eingänge zum oberen Gate sind dann 1 und 0, wodurch der Ausgang  $\bar{Q}$  auf 0 gezwungen wird. Dadurch werden beide Eingänge zum unteren Gate 0, was den Ausgang in 1 zwingt. Setzt man also  $S$  (auf 1), schaltet der Zustand von 0 in 1. Setzt man  $R$  auf 1, wenn sich die Latch im Zustand 0 befindet, tritt keine Wirkung ein, weil der Ausgang des unteren NOR-Gates für die Eingänge von 10 und die Eingänge von 11 je 0 ist.

Dadurch läßt sich leicht erkennen, daß das Setzen von  $S$  auf 1 im Zustand  $Q = 1$  wirkungslos bleibt, während das Setzen von  $R$  die Latch in den Zustand  $Q = 0$  treibt. Das heißt: Wird  $S$  vorübergehend auf 1 gesetzt, endet die Latch im Zustand  $Q = 1$ , ungeachtet des Zustands, in dem sie sich vorher befunden hat. Setzt man  $R$  vorübergehend auf 1, wird die Latch in den Zustand  $Q = 0$  gezwungen. Die Schaltung »merkt« sich, ob  $S$  oder  $R$  zuletzt an war. Anhand dieser Eigenschaft können wir Computer-Speicher entwickeln.

### Getaktete SR-Latches

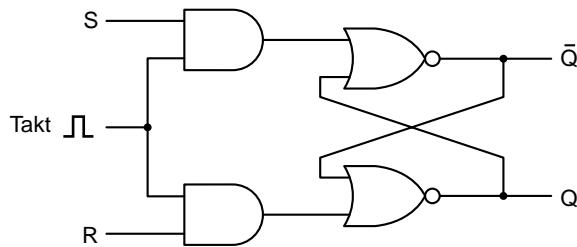

Latches müssen häufig so konstruiert werden, daß sie nur in ganz bestimmten Fällen ihren Zustand ändern können. Um dieses Ziel zu erreichen, ändern wir die Basisschaltung geringfügig, wie in Abb. 3.23 aufgezeigt, um eine sogenannte **Getaktete SR-Latch** (Clocked SR Latch) zu realisieren.

Abb. 3.23: Getaktete SR-Latch

Diese Schaltung verfügt über einen zusätzlichen Eingang, den Taktgeber, der normalerweise 0 ist. Ist der Taktgeber auf 0, geben beide AND-Gates unabhängig von S und R 0 aus, und die Latch ändert ihren Zustand nicht. Ist der Taktgeber 1, verschwindet die Wirkung der AND-Gates, und die Latch reagiert auf S und R. Das Taktsignal muß nicht durch eine Uhr gespeist werden. Die Begriffe **enable** und **strobe** sind weit verbreitet und bedeuten, daß der Takteingang 1 ist. Das bedeutet, daß die Schaltung auf den Zustand von S und R reagiert.

Bis jetzt haben wir das Problem, was passiert, wenn S und R 1 sind, übergangen. Und das aus gutem Grund: Die Schaltung wird nicht deterministisch, wenn R und S letztendlich auf 0 zurückkehren. Der einzige konsistente Zustand für  $S = R = 1$  ist  $Q = \bar{Q} = 0$ . Sobald aber beide Eingänge auf 0 zurückkehren, muß die Latch in einen ihrer beiden stabilen Zustände springen. Fällt ein Eingang vor dem anderen auf 0 zurück, gewinnt derjenige, der am längsten in 1 verbleibt. Wenn nämlich nur ein Eingang 1 ist, erzwingt er den Zustand. Kehren beide Eingänge gleichzeitig (was sehr unwahrscheinlich ist) auf 0 zurück, springt die Latch willkürlich in einen ihrer stabilen Zustände.

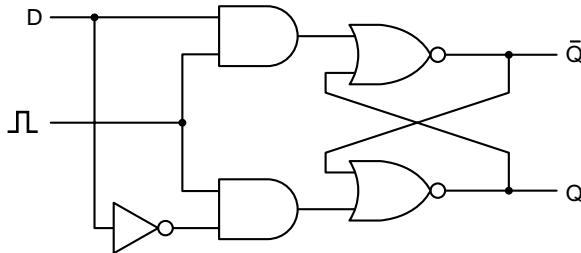

### Getaktete D-Latches

Das Problem der Zweideutigkeit (wenn  $S = R = 1$ ) der SR-Latch wird am besten gelöst, wenn man seinem Auftreten vorbeugt. Abb. 3.24 zeigt eine Latchschaltung mit nur einem Eingang D. Da der Eingang zum unteren AND-Gate immer das Komplement des Eingangs zum oberen ist, entsteht das Problem, daß beide Eingänge 1 sind, überhaupt nie. Wenn  $D = 1$  und der Taktgeber ist 1, wird die Latch in den Zustand  $Q = 1$  getrieben. Wenn  $D = 0$  und die Uhr ist 1, wird die Latch in den Zustand  $Q = 0$  versetzt. Anders ausgedrückt: Ist der Taktgeber 1, wird der aktuelle Wert von D als Muster abgetastet und in der Latch gespeichert. Diese Schaltung nennt man **getaktete D-Latch** (Clocked D Latch); sie ist ein echter 1-Bit-Speicher. Der gespeicherte Wert ist stets an Q verfügbar. Um den aktuellen Wert von D in den Speicher zu laden, wird ein positiver Impuls auf die Takteleitung gelegt.

Abb. 3.24: Getaktete D-Latch

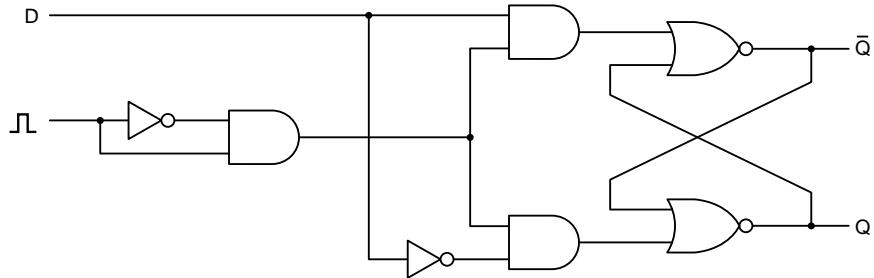

### 3.3.2 Flip-Flop-Schaltungen

Bei vielen Schaltungen muß man den Wert einer Leitung zu einem bestimmten Zeitpunkt abtasten und speichern. Bei dieser Variante – der **Flip-Flop-Schaltung** – tritt der Zustandsübergang nicht ein, wenn der Taktgeber 1 ist, sondern von 0 auf 1 (steigende Flanke) oder von 1 auf 0 (fallende Flanke) übergeht. Die Länge des Taktimpulses ist also unwichtig, solange die Übergänge schnell stattfinden.

Zur Verdeutlichung betrachten wir den Unterschied zwischen einer Flip-Flop-Schaltung und einer Latch genauer. Eine Flip-Flop-Schaltung wird **flankengesteuert** (edge-triggered), während eine Latch **pegelgesteuert** (level-triggered) wird. In der Literatur werden diese Begriffe häufig durcheinander gebracht. Viele Autoren verwenden »Flip-Flop-Schaltung« für eine Latch, und umgekehrt.

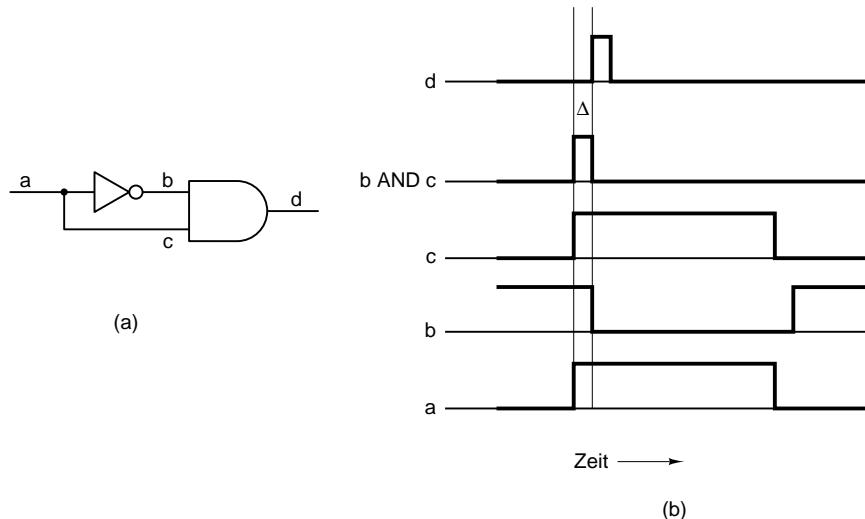

Für das Design einer Flip-Flop-Schaltung gibt es mehrere Ansätze. Hätte man beispielsweise die Möglichkeit, einen sehr kurzen Impuls auf der steigenden Flanke des Taktsignals zu erzeugen, könnte man diesen Impuls in eine D-Latch einspeisen. Diese Möglichkeit gibt es, und eine entsprechende Schaltung wird in Abb. 3.25(a) vorgestellt.

Auf den ersten Blick sieht es so aus, als ob der Ausgang des AND-Gates immer Null wäre, da das AND eines Signals zu seinem Gegenstück Null ist. Die Sache ist aber nicht so einfach. Durch den Inverter zieht sich eine kleine (ungleich Null) Ausbreitungsverzögerung, und genau diese Verzögerung sorgt für das Funktionieren der Schaltung. Angenommen, wir messen die Spannung der vier Meßpunkte  $a$ ,  $b$ ,  $c$  und  $d$ . Das an  $a$  gemessene Eingangssignal ist ein langer Taktimpuls (in Abb. 3.25(b) unten). Oberhalb dieses Impulses wird das an  $b$  gemessene Signal dargestellt. Letzteres ist sowohl invertiert als auch leicht verzögert, normalerweise um ein paar Nanosekunden, je nach dem benutzten Inverter.

Abb. 3.25: (a) Pulsgenerator; (b) Taktgabe an vier Punkten der Schaltung

Das Signal an  $c$  ist ebenfalls verzögert, aber nur um die Ausbreitungszeit des Signals (also der Lichtgeschwindigkeit). Ist die physische Entfernung zwischen  $a$  und  $c$  beispielsweise 20 Mikron, ergibt sich eine Ausbreitungsverzögerung von 0,0001 ns – sicherlich ein tolerierbarer Wert im Vergleich zu der Zeit, die das Signal für die Ausbreitung durch den Inverter braucht. Das Signal an  $c$  ist im Grunde also identisch mit dem an  $a$ .

Werden die Eingänge  $b$  und  $c$  zum AND-Gate mit AND verknüpft, ist das Ergebnis ein kurzer Impuls wie in Abb. 3.25(b), wobei die Breite des Impulses  $\Delta$  der Gate-Verzögerung des Inverters – normalerweise 5 ns oder weniger – entspricht. Der Ausgang zum AND-Gate ist nur dieser Impuls, verschoben um die Verzögerung des AND-Gates, wie in Abb. 3.25(b) dargestellt. Diese Zeitverschiebung bedeutet lediglich, daß die D-Latch in einer feststehenden Verzögerung nach der steigenden Flanke des Taktgebers aktiviert wird. Dies hat aber keine Wirkung auf die Pulsbreite. Bei einem Speicher mit einer Zykluszeit von 50 ns kann ein Impuls von 5 ns, der den Speicher anweist, wann die D-Leitung abzutasten ist, kurz genug sein. In diesem Fall kann die volle Schaltung Abb. 3.26 entsprechen. Dieses Flip-Flop-Schaltungdesign ist nett; weil es leicht verständlich ist, wäre in der Praxis aber viel zu einfach.

Abb. 3.26: D-Flip-Flop-Schaltung

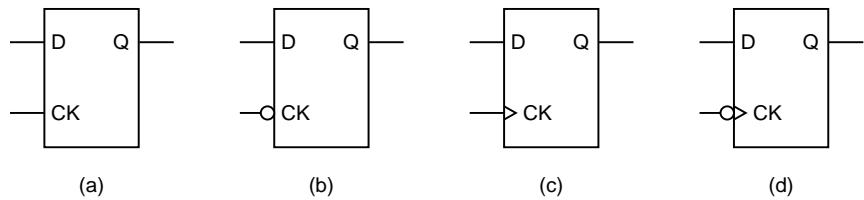

Abb. 3.27 zeigt die Standardsymbole für Latches und Flip-Flop-Schaltungen. In Abb. 3.27(a) sehen wir eine Latch, die in ihren Zustand eintritt, wenn der Taktgeber  $CK = 1$  ist. Abb. 3.27(b) zeigt im Gegensatz dazu eine Latch, deren Taktgeber normalerweise 1 ist, plötzlich aber auf 0 abfällt, um den Zustand von  $D$  zu laden. Die Abbildungen 3.27(c) und (d) stellen keine Latches, sondern Flip-Flop-Schaltungen dar, was durch Pfeilspitzen an den Takteingängen angedeutet ist. Abb. 3.27(c) ändert den Zustand auf der steigenden Flanke des Taktimpulses (Übergang von 0 auf 1), während Abb. 3.27(d) den Zustand auf der fallenden Flanke (Übergang von 1 auf 0) ändert. Viele, aber nicht alle Latches und Flip-Flop-Schaltungen haben auch  $\bar{Q}$  als Ausgang. Einige haben zwei zusätzliche Eingänge *Set* oder *Preset* (Zustand in  $Q = 1$  erzwingen) und *Reset* oder *Clear* (Zustand in  $Q = 0$  erzwingen).

Abb. 3.27: D-Latches und Flip-Flop-Schaltungen

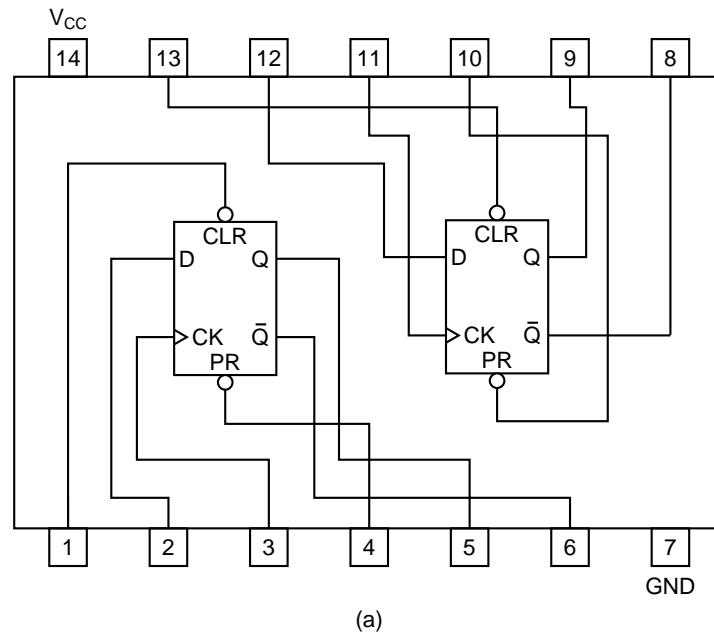

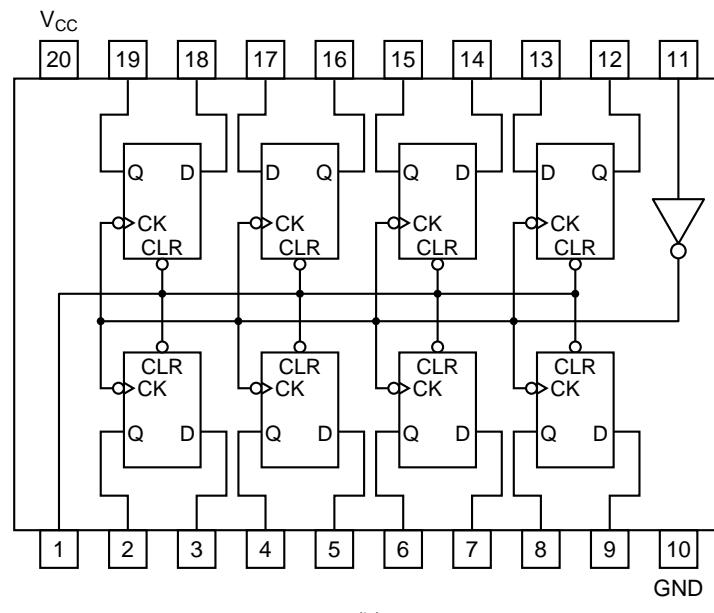

### 3.3.3 Register

Flip-Flop-Schaltungen gibt es in vielen verschiedenen Konfigurationen. Eine einfache mit zwei unabhängigen D-Flip-Flop-Schaltungen sowie Clear- und Preset-Signalen findet sich in Abb. 3.28(a). Obwohl sie auf einen 14-Pin-Chip gepackt wurden, haben die beiden Flip-Flop-Schaltungen aber keinen Zusammenhang. Eine recht unterschiedliche Anordnung weist die oktale Flip-Flop-Schaltung von Abb. 3.28(b) auf. Hier fehlen den acht (daher der Begriff »oktal«) D-Flip-Flop-Schaltungen nicht nur die  $\bar{Q}$ - und Preset-Leitungen. Alle Takteleitungen sind außerdem gruppiert und werden von Pin 11 gesteuert. Die Flip-Flop-Schaltungen selbst sind vom gleichen Typ wie Abb. 3.27(d), verfügen aber nicht über Inversionsblasen, weil der Inverter mit Pin 11 verbunden

ist, so daß die Flip-Flop-Schaltungen bei steigendem Übergang geladen werden. Alle acht Clear-Signale sind ebenfalls gruppiert, so daß alle Flip-Flop-Schaltungen in den 0-Zustand gezwungen werden, wenn Pin 1 in 0 wechselt. Falls Sie sich jetzt fragen, warum Pin 11 am Eingang und dann wieder bei jedem CK-Signal invertiert wird, hier die Antwort: Ein Eingangssignal hat möglicherweise nicht genug Strom, um alle acht Flip-Flop-Schaltungen zu betreiben, so daß der Eingangsinverter eigentlich als Verstärker verwendet wird.

Während die Takt- und Clear-Leitungen von Abb. 3.28(b) einerseits gruppiert wurden, um Pins einzusparen, wird der Chip bei dieser Konfiguration anders als bei acht unzusammenhängenden Flip-Flop-Schaltungen benutzt. Er dient als einziges 8-Bit-Register. Alternativ können zwei solche Chips parallel zur Bildung eines 16-Bit-Registers verwendet werden. Hierfür verbindet man ihre Pins 1 und 11. In Kapitel 4 werden Register und ihre Anwendungsbereiche genauer betrachtet.

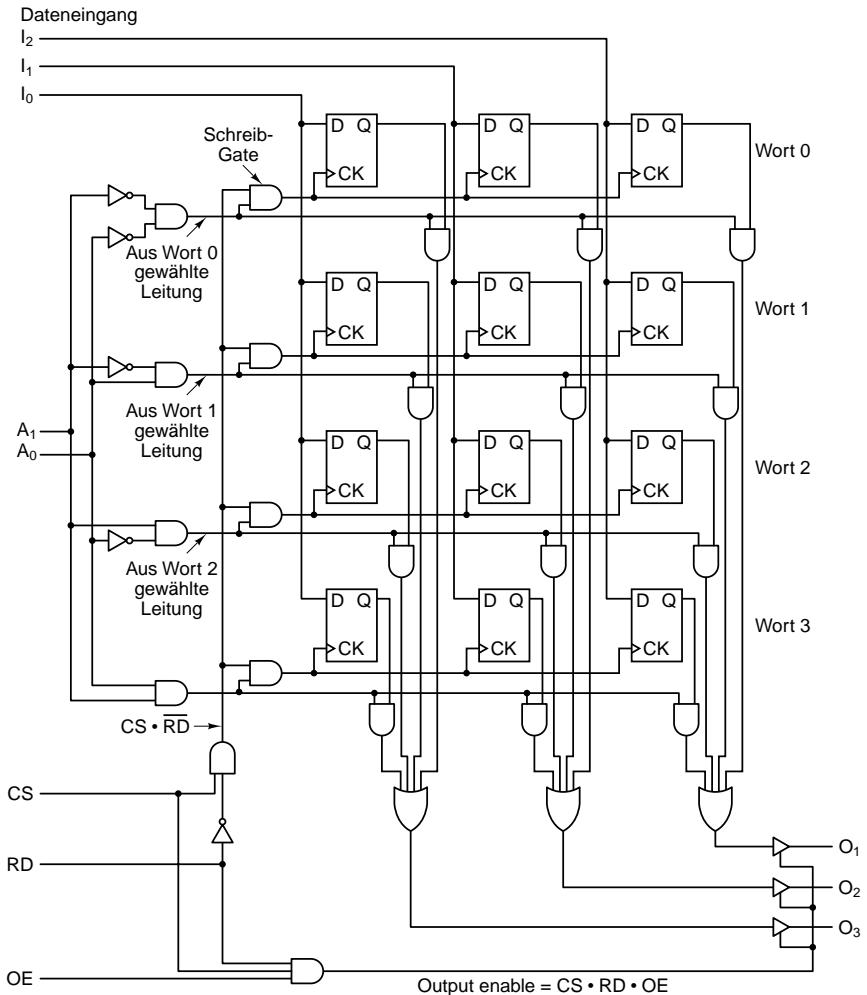

### 3.3.4 Speicherorganisation

Wir haben die Strecke vom einfachen 1-Bit-Speicher in Abb. 3.24 bis zum 8-Bit-Speicher in Abb. 3.28(b) zurückgelegt. Um große Speicher zu konstruieren, ist aber eine andere Organisation erforderlich, bei der man einzelne Wörter adressieren kann. Eine häufig benutzte Speicherorganisation, die dieses Kriterium erfüllt, ist in Abb. 3.29 dargestellt. Ein Speicher mit vier 3-Bit-Wörtern wird in diesem Beispiel gezeigt. Jede Operation liest oder schreibt ein volles 3-Bit-Wort. Während die gesamte Speicherkapazität von 12 Bits kaum mehr als unsere oktale Flip-Flop-Schaltung beträgt, benötigt sie weniger Pins; vor allem aber läßt sich das Design leicht auf große Speicher erweitern.

Der Speicher in Abb. 3.29 sieht auf den ersten Blick kompliziert aus, ist es dank seiner regelmäßigen Struktur aber nicht. Er hat acht Eingangs- und drei Ausgangsleitungen. Die drei Eingänge sind Daten:  $I_0$ ,  $I_1$  und  $I_2$ ; zwei sind für die Adressen  $A_0$  und  $A_1$ , und drei dienen der Steuerung: CS für Chip Select, RD zum Unterscheiden zwischen Lesen und Schreiben und OE für Output Enable. Die drei Ausgänge für Daten sind  $D_0$ ,  $D_1$  und  $D_2$ . Im Prinzip kann dieser Speicher in eine 14-Pin-Einheit gepackt werden, einschließlich Strom und Masse. Bei der oktalen Flip-Flop-Schaltung benötigt man hingegen 20 Pins.

Um diesen Speicherchip zu wählen, muß die externe Logik CS und auch RD zum Lesen auf High (logisch 1) und zum Schreiben auf Low (logisch 0) setzen. Die beiden Adreßleitungen müssen gesetzt werden, um anzugeben, welches der vier 3-Bit-Wörter gelesen oder geschrieben werden soll. Für eine Leseoperation werden die Dateneingangsleitungen nicht benutzt, das ausgewählte Wort wird aber auf die Datenausgangsleitungen gegeben. Bei einer Schreiboperation werden die auf den Dateneingangsleitungen vorhandenen Bits in das ausgewählte Speicherwort geladen. Die Datenausgangsleitungen werden nicht benutzt.

(a)

(b)

Abb. 3.28: (a) Duale D-Flip-Flop-Schaltung; (b) oktale Flip-Flop-Schaltung

Abb. 3.29: Logikdiagramm für einen 4x3-Speicher. Jede Reihe ist eines der vier 3-Bit-Wörter. Eine Lese- oder Schreiboperation liest bzw. schreibt immer ein ganzes Wort.

Betrachten wir Abb. 3.29 näher, um die Funktionsweise zu sehen. Die vier wortgewählten AND-Gates links vom Speicher bilden einen Dekodierer. Die Eingangsinverter wurden so angeordnet, daß jedes Gate durch eine andere Adresse eingeschaltet wird (Ausgang liegt auf High). Jedes Gate steuert eine wortgewählte Leitung, und zwar von oben nach unten für die Wörter 0, 1, 2 und 3. Wird der Chip für eine Schreiboperation ausgewählt, geht die mit  $CS \cdot \overline{RD}$  beschriftete vertikale Leitung auf High, wodurch eines der vier Schreib-Gates eingeschaltet wird, je nachdem, welche wortgewählte Leitung auf High ist. Die Ausgabe des Schreib-Gates steuert alle CK-Signale für das ausgewählte Wort, so daß die Eingangsdaten für das jeweilige Wort in die

Flip-Flop-Schaltungen geladen werden. Es erfolgt eine Schreiboperation nur in dem Fall, daß CS auf High und RD auf Low liegen, und auch dann wird nur das von  $A_0$  und  $A_1$  gewählte Wort geschrieben. Die übrigen Wörter werden nicht verändert.

Der Lesevorgang verläuft ähnlich wie der Schreibvorgang. Die Adresse wird genau so wie beim Schreiben dekodiert. Die Leitung  $CS \cdot \overline{RD}$  liegt aber auf Low, so daß alle Schreib-Gates ausgeschaltet sind und keine der Flip-Flop-Schaltungen geändert wird. Statt dessen aktiviert die wortgewählte Leitung die AND-Gates, die mit den Q-Bits des gewählten Worts verknüpft sind. Somit gibt das gewählte Wort seine Daten auf die OR-Gates aus, die vier Eingänge haben und unten in der Abbildung erscheinen, während die anderen drei Wörter Nullen ausgeben. Folglich ist die Ausgabe der OR-Gates mit dem im gewählten Wort gespeicherten Wert identisch. Die drei nicht gewählten Wörter tragen nichts zur Ausgabe bei.

Wir hätten auch eine Schaltung auslegen können, bei der die drei OR-Gates lediglich in die drei Ausgabedatenleitungen gespeist werden. Dies führt manchmal aber zu Problemen. Wir haben gezeigt, daß die Dateneingangs- und die Datenausgangsleitungen unterschiedlich sind. In echten Speichern werden aber die gleichen Leitungen benutzt. Hätten wir die OR-Gates mit den Datenausgangsleitungen verknüpft, würde der Chip versuchen, Daten auszugeben. Er würde also jede Leitung in einen bestimmten Wert zwingen, und dies sogar bei Schreiboperationen, was mit den Eingabedaten kollidieren würde. Aus diesem Grund ist eine Möglichkeit wünschenswert, die OR-Gates mit den Datenausgangsleitungen bei Leseoperationen zu verbinden, sie bei Schreiboperationen aber völlig zu trennen. Wir benötigen einen elektronischen Schalter, der eine Verbindung in wenigen Nanosekunden aufbauen und trennen kann.

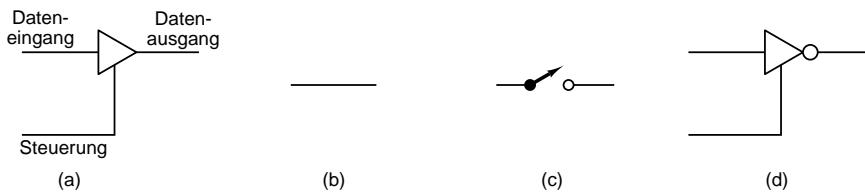

Zum Glück gibt es einen solchen Schalter. Abb. 3.30(a) zeigt das Symbol eines sogenannten **nicht invertierenden Puffers** (Noninverting Buffer). Er hat einen Dateneingang, einen Datenausgang und einen Steuereingang. Ist der Steuereingang auf High, agiert der Puffer wie ein Draht, was aus Abb. 3.30(b) ersichtlich wird. Liegt der Steuereingang auf Low, verhält sich der Puffer wie eine offene Schaltung, wie in Abb. 3.30(c). Dies hat den Effekt, als ob jemand den Datenausgang vom Rest der Schaltung mit einer Drahtschere abgeschnitten hätte. Im Gegensatz zum Gebrauch einer Drahtschere kann die Verbindung nachträglich aber in wenigen Nanosekunden wiederhergestellt werden, wenn man das Steuersignal wieder auf High setzt.

Abb. 3.30(d) zeigt einen **invertierenden Puffer** (Inverting Buffer), der sich wie ein normaler Inverter verhält, wenn die Steuerung auf High liegt, und den Ausgang von der Schaltung abtrennt, wenn die Steuerung auf Low ist. Beide Pufferarten sind **Tri-State-Geräte**, weil sie 0, 1 oder nichts (offene Schaltung) ausgeben können. Puffer verstärken außerdem Signale, so daß sie mehrere

Eingänge gleichzeitig steuern können. Sie werden manchmal aus diesem Grund in Schaltungen verwendet, obwohl ihre Schaltfähigkeiten nicht benötigt werden.

Abb. 3.30: (a) Nicht invertierender Puffer; (b) Wirkung von (a), wenn die Steuerung auf High liegt; (c) Wirkung von (a), wenn die Steuerung auf Low liegt; (d) invertierender Puffer

Wenden wir uns wieder der Speicherschaltung zu. Inzwischen dürfte klar sein, welchen Zweck die drei nicht invertierenden Puffer auf den Datenausgangsleitungen haben. Liegen CS, RD und OE auf High, ist auch das Ausgabesignal auf High, wodurch die Puffer eingeschaltet werden und ein Wort auf die Ausgangsleitungen gegeben wird. Liegt entweder CS oder RD oder OE auf Low, werden die Datenausgänge vom Rest der Schaltung getrennt.

### 3.3.5 Speicherchips

Angenehm an dem Speicher von Abb. 3.29 ist, daß er von seiner Größe her mühelos erweitert werden kann. Ursprünglich haben wir ihn mit  $4 \times 3$ , d.h. vier Wörtern von je 3 Bits, gezeichnet. Möchten wir ihn auf  $4 \times 8$  erweitern, müssen wir lediglich fünf weitere Spalten von je vier Flip-Flop-Schaltungen, fünf weitere Eingangsleitungen und fünf Ausgangsleitungen hinzufügen. Rüsten wir von  $4 \times 3$  auf  $8 \times 3$  auf, müssen wir vier weitere Zeilen von je drei Flip-Flop-Schaltungen und eine Adresszeile  $A_2$  hinzufügen. Bei dieser Struktur sollte die Anzahl der Wörter im Speicher eine Potenz von 2 betragen, um maximale Effizienz bei beliebiger Bitanzahl im Wort zu erreichen.

Da sich die integrierte Schaltkreistechnik gut zur Herstellung von Chips eignet, deren interne Struktur ein wiederkehrendes, zweidimensionales Muster aufweist, sind Speicherchips der ideale Anwendungsbereich dafür. Im Zuge der Verbesserung dieser Technik steigt die Bitanzahl, die man auf einen Chip packen kann, ständig, etwa um einen Faktor von Zwei alle 18 Monate (Moore-sches Gesetz). Durch größere Chips werden kleinere nicht immer veraltet, weil hinsichtlich Kapazität, Geschwindigkeit, Leistung, Preis und Schnittstellen viele Kompromisse gemacht werden müssen. In der Regel sind die derzeit erhältlichen größten Chips im Vergleich zu den älteren, kleineren pro Bit wesentlich teurer.

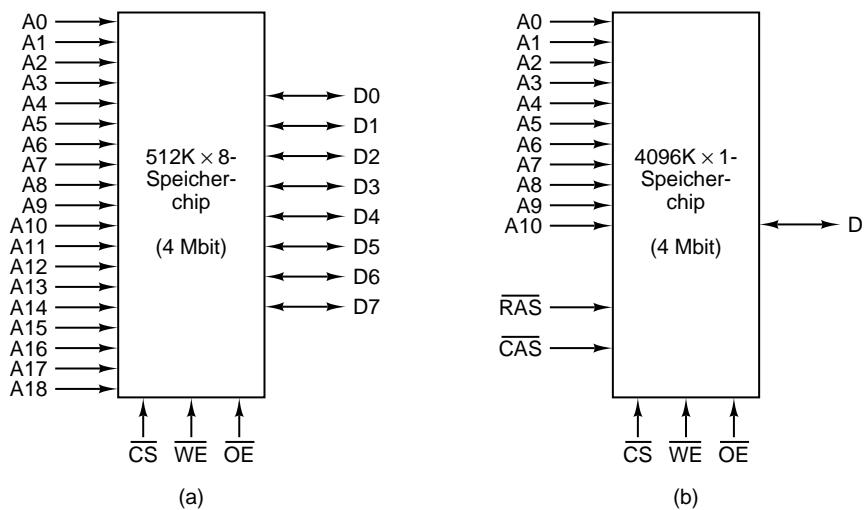

Der Chip kann für jede Speichergröße unterschiedlich organisiert werden. Abb. 3.31 zeigt zwei Aufbaumöglichkeiten eines 4-Mbit-Chips:  $512K \times 8$  und

$4096K \times 1$ . (Speicherchipgrößen werden normalerweise in Bits, und nicht in Bytes angeboten. Deshalb halten wir uns ebenfalls an diese Konvention.) In Abb. 3.31(a) sind 19 Adressleitungen erforderlich, um eines der  $2^{19}$  Byte zu adressieren. Zum Laden oder Speichern des ausgewählten Bytes braucht man acht Datenleitungen.

Abb. 3.31: Zwei Arten der Organisation eines 4-Mbit-Speicherchips

An dieser Stelle eine Anmerkung zur Terminologie: An einigen Pins erfolgt durch hohe Spannung eine Aktion. Bei anderen verursacht die niedrige Spannung eine Aktion. Um Verwechslungen zu vermeiden, sprechen wir im weiteren Verlauf davon, daß ein Signal **assertiert** (statt »auf High oder Low gesetzt wird«), um anzudeuten, daß es für das Bewirken einer Aktion gesetzt wird. Bei einigen Pins bedeutet Asserieren, daß sie auf High gelegt werden. Bei anderen bedeutet es, daß der Pin auf Low gesetzt wird. Bei Pins, die auf Low liegen, werden die Signalbezeichnungen mit einem Überstrich angegeben. Ein Signal namens CS wird also auf High und eines mit der Bezeichnung  $\overline{CS}$  auf Low gelegt. Das Gegenteil von Asserieren ist **Negieren**. Wenn nichts Besonderes passiert, werden Pins negiert.

Zurück zu unserem Speicherchip. Da ein Computer normalerweise viele Speicherchips hat, ist ein Signal erforderlich, um den aktuell benötigten Chip zu wählen, damit er und kein anderer reagiert. Das Signal  $\overline{CS}$  (Chip Select) erfüllt diesen Zweck. Es wird zur Chipaktivierung asseriert. Außerdem muß man zwischen Lese- und Schreiboperationen unterscheiden können. Das Signal  $\overline{WE}$  (Write Enable) wird benutzt, um zu bezeichnen, daß Daten geschrieben, und nicht gelesen werden. Schließlich wird das Signal  $\overline{OE}$  (Output Enable) zur Steuerung der Ausgangssignale asseriert. Bei Nichtasserierung wird der Chipausgang von der Schaltung getrennt.

In Abb. 3.31(b) wird ein anderes Adressierschema benutzt. Intern ist dieser Chip als Matrix von  $2048 \times 2048$  1-Bit-Zellen organisiert, die 4 Mbit ergeben. Zur Chipadressierung wird zuerst eine Zeile ausgewählt, indem man ihre 11-Bit-Zahl auf die Adreßpins legt. Dann wird  $\overline{RAS}$  (Row Address Strobe) asseriert. Anschließend wird eine Spaltennummer auf die Adreßpins gelegt und  $\overline{CAS}$  (Column Address Strobe) asseriert. Der Chip reagiert durch Annahme oder Ausgabe eines Datenbits.

Große Speicherchips werden oft als  $n \times n$ -Matrizen ausgelegt, die durch Zeile und Spalte adressiert werden. Dieser Aufbau reduziert die benötigte Pinanzahl, verlangsamt aber auch die Adressierung des Chips, da zwei Adressierzyklen erforderlich sind – einer je Zeile und Spalte. Um einen Teil der Geschwindigkeit zurückzugewinnen, können Speicherchips mit einer Zeilenadresse, gefolgt von mehreren Spaltenadressen, eingerichtet werden, so daß aufeinanderfolgende Bits in einer Reihe adressiert werden können.

Vor Jahren wurden die größten Speicherchips allgemein wie in Abb. 3.31(b) ausgelegt. Im Zuge der Vergrößerung von Speicherwörtern von 8 auf 32 Bits und mehr wurden 1 Bit große Chips unpraktisch. Um einen Speicher mit einem 32-Bit-Wort aus  $4096K \times 1$  großen Chips zu entwickeln, werden 32 parallele Chips benötigt. Diese 32 Chips haben eine Gesamtkapazität von mindestens 16 Mbyte, während bei Verwendung von  $512K \times 8$ -Chips nur vier parallele Chips nötig und kleine Speicher, etwa 2 Mbyte, möglich sind. Um die Verwendung von 32 Chips für einen Speicher zu vermeiden, haben die meisten Chiphersteller heute Chipfamilien mit Breiten von 1, 4, 8 und 16 Bits.

### 3.3.6 RAM und ROM

Alle Speicher, die wir bisher untersucht haben, können lesen und schreiben. Solche Speicher nennt man **RAMs** (Random Access Memories) – eine falsche Bezeichnung, weil alle Speicherchips zufallsgesteuerten Zugriff haben. RAMs gibt es in zwei Varianten: statisch und dynamisch. **Statische RAMs (SRAMs)** werden intern mit Schaltungen realisiert, die unserer grundlegenden D-Flip-Flop-Schaltung ähneln. Diese Speicher haben die Fähigkeit, ihre Inhalte zu behalten, solange der Strom fließt: Sekunden, Minuten, Stunden oder gar Tage. Statische RAMs sind sehr schnell. Die typischen Zugriffszeiten betragen nur wenige Nanosekunden. Aus diesem Grund sind RAMs als Cache-Speicher der Ebene 2 (Cache Level-2) sehr beliebt.

Demgegenüber werden in **dynamischen RAMs (DRAMs)** keine Flip-Flop-Schaltungen benutzt. Ein dynamischer RAM besteht aus einer Reihe von Zellen, wobei jede Zelle einen Transistor und einen winzigen Kondensator enthält. Kondensatoren können ge- und entladen werden, so daß sich Nullen und Einsen speichern lassen. Da elektrische Ladung zu Kriechverlusten neigt, muß jedes Bit in einem dynamischen RAM zur Vermeidung von Datenverlust alle paar Millisekunden **aufgefrischt** (nachgeladen) werden. Weil sich externe

Logik um die Auffrischung kümmern muß, erfordern dynamische RAMs komplexere Schnittstellen als statische. Dieser Nachteil gleicht sich in vielen Anwendungen aber durch ihre größeren Kapazitäten aus.

Dynamische RAMs benötigen nur einen Transistor und einen Kondensator pro Bit (gegenüber sechs Transistoren pro Bit beim besten statischen RAM). Deshalb haben dynamische RAMs eine sehr hohe Dichte (viele Bits pro Chip). Aus diesem Grund werden Hauptspeicher fast immer mit dynamischem RAM realisiert. Diese große Kapazität hat aber ihren Preis: Dynamische RAMs sind langsam (zg Nanosekunden). Durch eine Kombination aus statischem RAM-Cache und dynamischem RAM-Hauptspeicher wird versucht, die guten Eigenschaften von beiden zu nutzen.

Dynamische RAM-Chips sind in verschiedenen Typen erhältlich. Der älteste Typ ist der **FPM-DRAM** (FPM = Fast Page Mode); er ist immer noch in Gebrauch. Intern ist dieser DRAM als Bitmatrix organisiert. Er funktioniert mittels Präsentation einer Leitungsadresse durch die Hardware. Dann werden die Spaltenadressen durchlaufen, wie in Zusammenhang mit  $\overline{RAS}$  und  $\overline{CAS}$  von Abb. 3.31(b) beschrieben wurde.

FPM-DRAMs werden nach und nach durch den **EDO-DRAM** (Extended Data Output) abgelöst. Beim EDO-DRAM kann eine zweite Speicherreferenz vor Beendigung der ersten beginnen. Dieses einfache Pipelining beschleunigt eine einzelne Speicherreferenz nicht, verbessert aber die Speicherbandbreite, d.h., ein Durchschleusen von mehr Wörtern pro Sekunde ist möglich.

FPM- und EDO-Chips sind asynchron, was bedeutet, daß die Adreß- und Datenleitungen nicht durch einen einzigen Taktgeber gesteuert werden. Demgegenüber ist der **SDRAM** (Synchronous DRAM) eine Mischung aus statischem und dynamischem RAM; er wird durch einen einzelnen, synchronen Taktgeber gesteuert. SDRAMs werden häufig in großen Cache-Speichern benutzt und gelten als die bevorzugte Technologie für Hauptspeicher der Zukunft.

RAMs sind nicht die einzige Art von Speicherchips. In vielen Anwendungen, z.B. Spielzeugen, Elektrogeräten und Autos, müssen das Programm und ein Teil der Daten auch bei ausgeschaltetem Strom gespeichert bleiben. Außerdem werden weder das Programm noch die Daten nach der Installation jemals geändert. Diese Anforderungen haben zur Entwicklung von **ROMs** (Read-Only Memories) geführt, die weder absichtlich noch anderweitig geändert oder gelöscht werden können. Beim ROM werden die Daten bei der Herstellung des ROMs auf der Oberfläche eingebrannt. Will man das in einem ROM gespeicherte Programm ändern, muß man den gesamten Chip ersetzen. Es gibt keine andere Änderungsmöglichkeit.

ROMs sind viel billiger als RAMs, wenn man sie in großen Mengen bestellt, weil sich durch die Menge die Kosten für die Herstellung der Maske amortisieren. Sie sind aber unflexibel, weil man sie nach der Herstellung nicht ändern kann. Außerdem können zwischen der Bestellung und der Auslieferung

viele Wochen vergehen. Um es Unternehmen zu vereinfachen, neue ROM-basierte Produkte zu entwickeln, wurde der **PROM** (Programmable ROM) erfunden. Dieser Chip arbeitet wie ein ROM, ausgenommen, daß man ihn (einmal) im Feld programmieren kann, wodurch sich die Vorlaufzeit erheblich verkürzt. Viele PROMs enthalten eine Reihe winziger Sicherungen. Diese Sicherungen können selektiv durchgebrannt werden, wenn man eine Zeile und Spalte wählt und dann auf einen der Pins Hochspannung zur Zerstörung einer bestimmten Sicherung aufbringt.

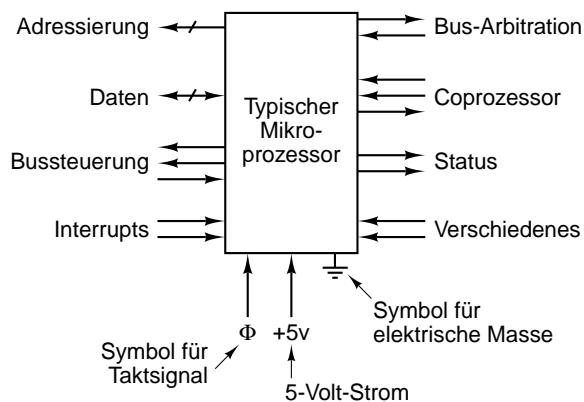

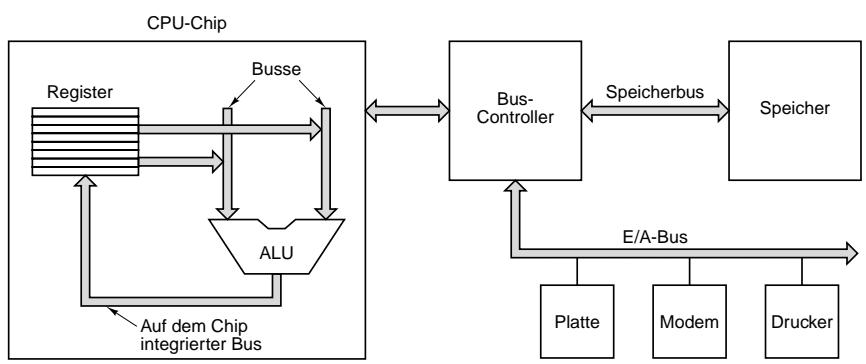

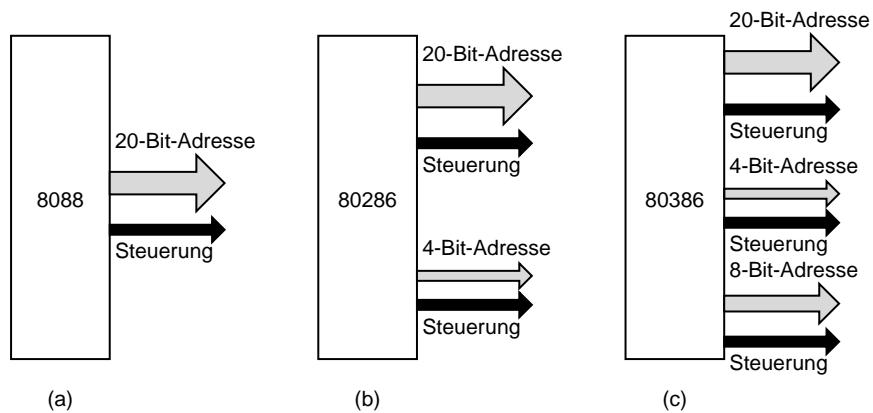

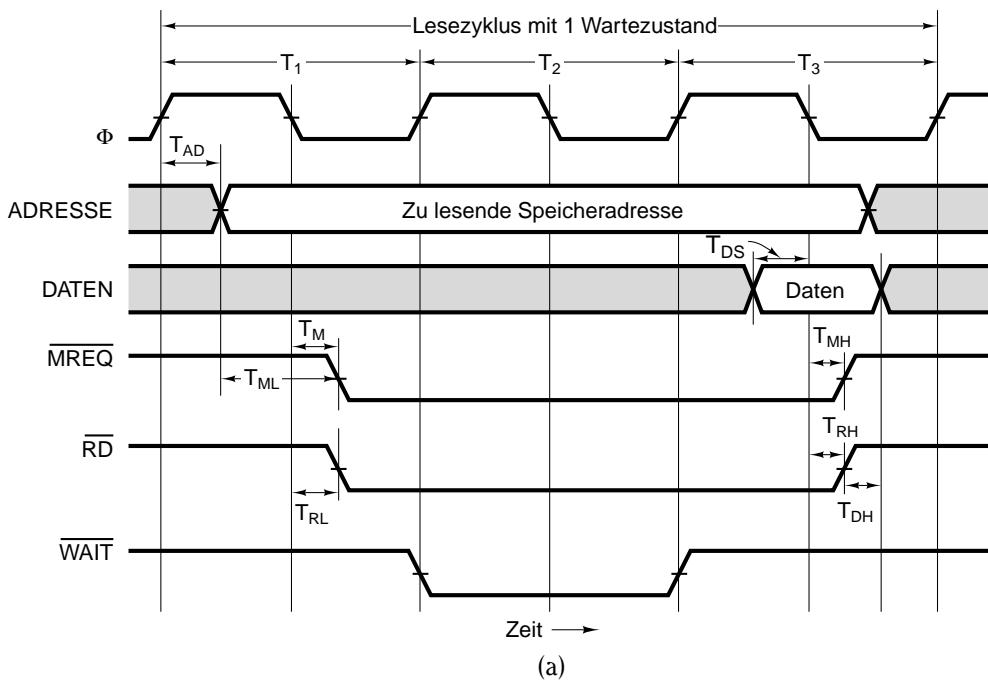

Die nächste Entwicklung dieser Linie war der **EPROM** (Erasable PROM), den man im Feld nicht nur programmieren sondern auch löschen kann. Wird das Quarzfenster in einem EPROM 15 Minuten lang einem starken ultravioletten Licht ausgesetzt, werden alle Bits auf 1 gesetzt. Gibt es im Verlauf des Designzyklus viele Änderungen, sind EPROMs weitaus wirtschaftlicher als PROMs, weil man sie wiederverwenden kann. EPROMs sind normalerweise als statische RAMs organisiert. Der 4-Mbit-EPROM 27C040 basiert beispielsweise auf einer Struktur wie in Abb. 3.31(a), die für einen statischen RAM typisch ist.