# DYNAMIC MODELS FOR SUBSTRATE COUPLING IN MIXED-MODE SYSTEMS

João M. S. Silva

jmss@algos.inesc-id.pt

INESC ID Lisboa

Instituto Superior Técnico

Technical University of Lisbon

R. Alves Redol, 9, Sala 133, 1000-029 Lisboa, Portugal

### Luís Miguel Silveira

Ims@inesc-id.pt

Cadence Laboratories

INESC ID Lisboa

Instituto Superior Técnico

Technical University of Lisbon

R. Alves Redol, 9, Sala 136, 1000-029 Lisboa, Portugal

#### Abstract

In modern monolithic integrated circuits, substrate coupling is a major concern in mixed-mode systems design. Noise injected into the common substrate by fast switching digital blocks may affect the correct functioning or performance of the overall system. Verification of such systems implies the availability of accurate and simulation-efficient substrate coupling models. For frequencies up to a few gigahertz pure resistive models are considered sufficient, but increasing frequencies of operation imply that capacitive coupling analysis also becomes mandatory.

In this paper, we motivate the use of dynamic resistive-capacitive (RC) models of substrate coupling as a natural extension to the standard purely resistive models. We propose an extraction methodology that starts from information about the process parameters and the contact layout of the circuit, and leads to a contact-to-contact RC element model. The underlying algorithm is based upon a Finite Difference discretization of the substrate, leading to a large tridimensional mesh which is solved by means of a fast Multigrid algorithm.

The proposed model is trivially incorporated into circuit simulation tools. Comparisons are also made to a model obtained using standard model order reduction algorithms and it is shown to be of similar accuracy. The formulation proposed can accurately model substrate coupling effects for frequencies up to several tens of gigahertz.

## 1. Introduction

Substrate behavior in integrated circuits has long ceased to be considered as a perfect insulator [Joardar, 1994; Kup et al., 1991; Gharpurey, 1995]. As MOS process' transistor channel widths decrease to the size of a few nanometers, digital clock frequencies have been steadily increasing, so that current injection into the polysilicon substrate becomes a great concern. Along with technology miniaturization, die area has shrunk on behalf of package count and production yield purposes. Consequently, different cells and blocks are built closer to each other, in a way that facilitates injected substrate currents to migrate among the substrate layers and reach arbitrarily distant parts of the circuit [Gharpurey, 1995; Su et al., 1993; Verghese, 1995].

Current injection into the substrate can occur through active and channel areas, as well as through substrate and well contact ties. Such currents can cause substrate voltage fluctuations leading to changes in the device's bulk-to-substrate voltage. For purely digital circuits, this is still not a major concern since, from a functional perspective, digital logic is somewhat immune to substrate voltage fluctuations. However, performance degradation can still occur as millions of logic gates switching induces significant additional noise and can cause power supply voltage levels to fluctuate. This can affect logic gates delay and circuit overall time performance.

It is however in the context of mixed-signal design that the issue of substrate coupling has received the most attention in recent years. Industry trends aimed at integrating higher levels of circuit functionality, resulting from an emphasis on compactness in consumer electronic products, and a widespread growth and interest in wireless communications, have triggered a proliferation of mixed analog-digital systems. The design of such systems is an increasingly difficult task owing to the various coupling problems that result from the combined requirements for high-speed digital and high-precision analog components.

Analog circuitry relies on accurate levels of currents and voltages, so that analog transistors are correctly biased and projected performance is met. When substrate injected currents migrate through the substrate, substrate voltages fluctuate, causing havoc in sensitive analog transistors and possibly leading to malfunctioning circuitry [Gharpurey, 1995; Su et al., 1993; Johnson et al., 1984; Nauta and Hoogzaad, 1997].

Analyzing the effects of substrate coupling requires that a model of such couplings is obtained and used in a verification framework. Typically such a verification is done at the electrical level by means of a circuit simulator. Therefore, the usual strategy is to generate an electric coupling model and feed it to a circuit simulator together with the remaining circuitry. Since potentially,

everything couples to everything else through the common substrate, leading to extremely large models, special care must be taken to make sure that the model is accurate but will not unnecessarily slow down the verification step. This has traditionally been achieved in a variety of ways all aiming at a simplified model.

When generating the model, a common simplifying assumption is to consider that the major coupling mechanism is due to the finite resistivity of the substrate and derive a resistive model. Such an approximation is valid when the dielectric relaxation time of the layers composing the substrate translates into an insignificant susceptance at the frequencies of interest. Thus, such an approximation becomes questionable beyond a few gigahertz, specially since harmonics of significant amplitude, generated by circuit nonlinearities, may fall in the range of frequencies where reactive effects are of importance.

In this paper, a methodology is proposed for generating dynamic resistive-capacitive (RC) models of substrate coupling. The methodology proposed for model extraction is detailed and the model is analyzed in terms of its validity and accuracy. In section 2, the mechanisms for substrate coupling are briefly discussed and background work in this area is reviewed. In Section 3 the proposed model extraction algorithm is presented and its extension to dynamic analysis is detailed. In Section 4 the validity, accuracy and relevance of the obtained model is discussed through some example simulations. The model obtained is also compared to those generated using standard model order reduction techniques and it is shown to be of similar accuracy. Finally in Section 5 some conclusions are drawn.

# 2. Background

# **Substrate Coupling Mechanisms**

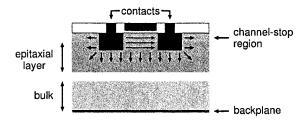

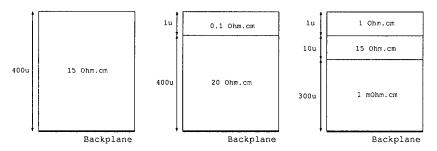

Coupling through the substrate occurs, mainly, due to substrate finite resistivity. Devices built into the same substrate are consequently not perfectly isolated from each other. Considering a typical substrate profile like the one shown in Figure 1, MOS transistors are based on channel formation, so substrate resistivity is not desired to be infinite. However, when a transistor is on, while current flows through the corresponding channel, part of it is injected into the substrate and is free to migrate to arbitrarily distant substrate zones. Another equally important type of noise injection into the substrate occurs through VDD and GND contact ties. When devices switch, currents are drawn from or injected into the power supply which typically also bias the substrate. In this manner, current is also directly injected into the substrate.

At higher frequencies, when active areas are charged and discharged, sourcebulk and drain-bulk parasitic capacitances show a lower impedance and current is also directly injected into the substrate by these active areas.

Figure 1. Depiction of typical substrate profile.

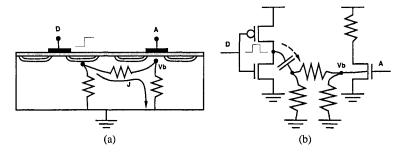

The fact that such currents are in a sense free to roam around the substrate and may be captured wherever appropriate conditions are met, makes the verification process much harder. While it is true that most of the coupling may occur locally, designer experience and good design practices lead to designs where such local couplings are explicitly minimized. As a consequence, the assumption of mostly local coupling is not necessarily valid and unexpected long range couplings may appear where least expected. As such, not only is it mandatory that some kind of substrate model be used to account for substrate couplings between different blocks built on the same substrate, but that model must also account for all or at least large portions of the substrate. Substrate coupling mechanism and corresponding electric model examples are shown in Figure 2.

Figure 2. Example of resistive coupling: current injection mechanism into the substrate (a) and corresponding electric model (b).

## **Previous Work**

Previous work in the area of substrate model extraction is profuse. The general trend, however, has been toward the generation of resistive coupling models. Capacitive coupling through the substrate has been generally considered neglectable based on the properties of current technologies which present a sil-

icon relaxation time in the order of picoseconds. This fact is said to typically limit the validity of pure resistive models to be up to the order of gigahertz. As today's frequency of operation increases, the gigahertz frontier has clearly been surpassed, so that mixed systems with aggressive fast digital components may require more accurate modeling.

Several extraction methodologies were studied in the past and, based on them, several extracting tools were developed. The simplest modeling methodologies consist on finding coupling elements based on heuristic rules. Such methods are very attractive since the extraction overhead is minimal and they lead to simple first order models which also have low simulation costs [Su et al., 1993; Johnson et al., 1984; Nauta and Hoogzaad, 1997; van Genderen et al., 1996; Mitra et al., 1995]. These models are, however, generally very imprecise. Furthermore, heuristic models are only really useful to the designer, for they are unable to account for higher order effects and, in fact, rely on designer's experience to prune out the expected relevant couplings [Phillips and Silveira, 2001]. Moreover, once that is accomplished they do not provide any form of verification as to whether the performed approximation enables correct circuit simulation. With the geometric complexity and dimensions of actual circuits, heuristic models are unable to predict the real functioning of the full system substrate interactions and such models are somewhat imprecise and unreliable.

On the other hand, methodologies that avoid a-priori heuristic pruning and work at the electrical level directly are typically based on a full description of the media and all the possible couplings. A problem that arises from model extraction in those cases is the extraction time and the size of the final model. Coupling can occur from any substrate contact to any other, so that a full interaction matrix can be drawn from it.

Several methods have been proposed to generate such a model. One of these families of methods are Boundary Element Methods (BEM). In BEM methods, only the surface of the substrate contacts is discretized which leads to a system of equations that corresponds to small but full matrices. Extraction of such models requires intensive computations which restrains the range of applicability of this method to small and medium sized circuits [Smedes et al., 1995; Gharpurey and Meyer, 1995; Verghese and Allstot, 1995]. Fortunately, significant progress in BEM methods performance has been lately achieved [Costa et al., 1998; Chou and White, 1998; Kanapka et al., 2000].

A different but also efficient family of extraction methods are Finite Difference (FD) or Finite Element Methods (FEM). In these methods, the whole tridimensional volume of the substrate is discretized leading to large but sparse matrices. The sparsity pattern of these matrices can be taken advantage of depending on the system solving methods which are used. Notwithstanding, FEM still face difficulties, mostly related to memory resources, due to the large matrices

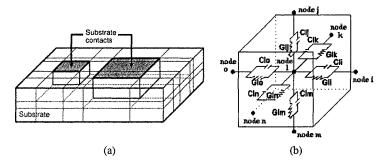

Figure 3. (a) FD method discretization and (b) resulting substrate resistive-capacitive (RC) model.

required. This type of methods have also been recently enhanced with fast solution techniques [Clement et al., 1994; Wemple and Yang, 1995; Stanisic et al., 1994; Kanapka et al., 2000; Silveira and Vargas, 2002; Silva, 2003].

As mentioned previously, RC models of substrate coupling are less common that purely resistive models. Notwithstanding, previous work has been published in this field that considers the needs for capacitive effects in substrate coupling [Clement et al., 1994; Gharpurey and Hosur, 1997]. RC models are also partially used in some commercial tools, typically in an heuristic way, but there is no systematic assessment of their relevance. In this work, a Finite Difference method for the extraction of resistive-capacitive (RC) substrate models is proposed and its usefulness and validity are assessed.

#### 3. Substrate Model Extraction

In the following, our method for the extraction of a model of the couplings through the substrate is presented.

#### Finite Difference Tridimensional Model

We use a FD method accounting for geometric discretization accuracy. This implies a discretization of the substrate volume into a large number of small cuboid elements. An example of such a discretization is shown in Figure 3-a) where nodes on a tridimensional mesh are immediately visible. This method provides infinite accuracy when discretization spacing tends to zero.

The next step is to model the whole substrate by applying electromagnetic laws to each cuboid element (which we will call node) of the mesh. Starting from Maxwell's equations and neglecting the effect of magnetic fields, we use the identity  $\nabla(\nabla \times a) = 0$  and Ampère's Law to write:

$$\nabla J + \nabla \frac{\partial D}{\partial t} = 0 \tag{1}$$

where J is the current density and D is the electric displacement. Equation (1) is the continuity equation and expresses the conservation of electric charge. Recalling that:

$$\begin{cases}

J = \sigma E \\

D = \varepsilon E

\end{cases}$$

(2)

where  $\sigma$  and  $\varepsilon$  are the conductivity and the permittivity of the medium, respectively, and E the electric field, Equation (1) can also be written as:

$$\sigma \nabla E + \varepsilon \frac{\partial \nabla E}{\partial t} = 0. \tag{3}$$

Assuming an homogeneous medium in each substrate layer, consider a cuboid whose center is node i with neighbor cuboid whose center is j. If  $E_{ij}$  denotes the electrical field normal to the cuboid side surface between nodes i and j, the Finite Difference approximation leads to:

$$E_{ij} \approx \frac{V_i - V_j}{l_{ij}} \tag{4}$$

where  $l_{ij}$  is the distance between adjacent nodes i and j, and  $V_i$  and  $V_j$  the scalar potentials at those nodes. At this point, a simple box integration technique can be used to solve Equation (3) since the substrate is spatially discretized. Applying Gauss' law:

$$\nabla E = \frac{r}{\varepsilon} \tag{5}$$

where r is the charge density of the medium (time dependence omitted but implicit). From the divergence theorem, we know that:

$$\int_{\mathcal{S}_{i}} E \, d\mathcal{S}_{i} = \int_{\mathcal{V}_{i}} \nabla E d\mathcal{V}_{i} = \int_{\mathcal{V}_{i}} \frac{r}{\varepsilon} \, d\mathcal{V}_{i} \tag{6}$$

where  $V_i$  is the volume of the *i*-th cuboid and  $S_i$  its surface. The left hand side of Equation (6) can be approximated as:

$$\int_{\mathcal{S}_i} E \, d\mathcal{S}_i \approx \sum_j E_{ij} \mathcal{S}_{ij} = \frac{r}{\varepsilon} \, \mathcal{V}_i \tag{7}$$

where the summation is performed on cuboids that are neighbors of cuboid i, and  $S_{ij}$  is the common surface between cuboids i and j. Now using Equation (7) in (5) leads to:

$$\nabla E = \frac{1}{\mathcal{V}_i} \sum_{j} E_{ij} \mathcal{S}_{ij}. \tag{8}$$

The above derivation assumed a common resistivity, i.e. a single layer. The extension to multiple layers is trivially handled by assuring that the layer interface is delimited with mesh nodes.

Finally, replacing Equations (4) and (8) into (3) results in:

$$\sum_{j} \left[ G_{ij} (V_i - V_j) + C_{ij} \left( \frac{\partial V_i}{\partial t} - \frac{\partial V_j}{\partial t} \right) \right] = 0$$

(9)

where:

$$\begin{cases}

G_{ij} = \sigma \frac{S_{ij}}{l_{ij}} \\

C_{ij} = \varepsilon \frac{S_{ij}}{l_{ij}}

\end{cases}$$

(10)

Equation (9) can readily be interpreted in terms of the electrical model depicted in Figure 3-b). In fact, applying Nodal Analysis (NA) to the 3D mesh model (9) leads to the following system of equations:

$$(sC+G)V = I (11)$$

where C and G are, respectively, the capacitance and conductance matrices of the system, V is the voltage on all nodes of the discretization mesh and I the corresponding injected currents. From (9), entries of G and C in (11) can be approximated with Equation (10) here applied to each element in the model.

The size of the model in (11) is directly determined by the chosen discretization. For very fine discretizations, required for accuracy considerations, this implies that the model in (11) could be very large indeed. For a discretization of dx, dy, dz in each direction, the matrix size will be  $N = dx \times dy \times dz$ . On the other hand, one should note that the model is very sparse, since matrices C and G correspond to the 3D discretization pencil and only have at most 7 non-zero entries in each row or column (corresponding, for each node, to the diagonal entry and to entries for each of the 6 neighbor nodes in a 3D mesh).

#### Circuit-level Model Extraction

Using the 3D mesh model from (9) in any electrical simulator is prohibitive. As such, a reduced model must be sought. A possible solution to this problem

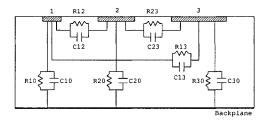

Figure 4. RC model for a three contact configuration.

is to apply standard model order reduction techniques to the problem and obtain a reduced model [Feldmann and Freund, 1995; Silveira et al., 1995; Odabasioglu et al., 1998]. For such methods, the size of the resulting model is directly proportional to the product of the approximation order by the number of ports (inputs/outputs or contacts in our case). This causes two potential problems. First, an appropriate reduction order must be devised. Second, for systems with large numbers of contacts, small increases in the approximation order lead to large increases in model size and potentially to overly large models. We will come back to this discussion in the next section, but for the time being we propose a constructive methodology and seek to obtain a simple model whose size is uniquely determined by the number of substrate contacts and thus independent from the chosen discretization or any other parameter. We will illustrate this methodology by means of a simple example such as the one depicted in Figure 4 for a three-contact setup. Furthermore, we note this model is an obvious extension of the typical resistive models whereby a coupling resistance is computed between pairs of contacts. Here that resistance is replaced with the parallel impedance of a resistor and a capacitor.

Assuming a generic model similar to that of Figure 4, and using NA, the corresponding system of equations is given by:

$$Y_c(s)U = (sC_c + G_c)U = J$$

(12)

where  $Y_c$  is the admittance of the contact's system,  $C_c$  and  $G_c$  are, respectively, the capacitive and resistive coupling elements between contacts, and U and J are the vectors of contact voltages and injected currents. This system is naturally analog to (11) but much smaller.

The substrate model in (12) can readily be obtained from the 3D model in (11) by means of simple computations. An algorithm to perform this task is presented in Algorithm 1. Again, not surprisingly, this is the obvious extension of the standard FD procedure used nowadays to obtain resistive substrate models [Clement et al., 1994; Silveira and Vargas, 2002; Silva, 2003].

The computations can be simplified by assuming sinusoidal steady state and rewriting (12) as:

$$(j\omega C_c + G_c) \|U\| e^{j\omega t + \phi_1} = \|J\| e^{j\omega t + \phi_2}$$

(13)

leading to:

$$(j\omega C_c + G_c)\|U\|e^{\phi_1} = \|J\|e^{\phi_2} \Leftrightarrow (j\omega C_c + G_c)\overline{U} = \overline{J}. \tag{14}$$

If the imposed voltage in contact k is  $U_k=1$   $sin(j\omega t+0)$  then only the k-th component of  $\overline{U}$  in (14) is at 1 volt and thus  $\overline{J}$  is equal to the k-th column of  $G_c+j\omega C_c$ .

This process can be repeated as many times as the number of contacts so that the full admittance matrix  $Y_c = G_c + j\omega C_c$  is formed, one column at a time. This may, in general, require complex numbers arithmetic. The cost of computing the contact model,  $Y_c(s)$ , for a system of m contacts is thus equal to m times the cost of solving the 3D mesh to determine the node voltages. This can be performed very efficiently by means of a fast Multigrid algorithm with a cost of  $\mathcal{O}(N)$  per solve [Silveira and Vargas, 2002; Silva, 2003], albeit using complex arithmetic.

## Algorithm 1 Admittance model extraction algorithm.

For contact k = 1 ... number of contacts:

- 1 Put contact k nodes at a pre-determined voltage (e.g. 1 V);

- 2 Using Norton's equivalent, obtain the currents injected into adjacent nodes;

- 3 Solve the 3D system (11) obtaining all nodes voltages, V;

- 4 From *V* and 3D model admittances use Ohm's law to compute current injected in all contact nodes;

- 5 Use Gauss' law and sum injected node currents to obtain contact injected currents *J*:

- 6 By Equation (12) and as only nodes on contact k had a fixed voltage, k-th column of  $G_c + C_c$  equals J.

| Contact 1 | Contact 2 | Resistance             | Capacitance |

|-----------|-----------|------------------------|-------------|

| 1         | backplane | 23 kΩ                  | 687 aF      |

| 1         | 2         | 243 kΩ                 | 65.0 aF     |

| 1         | 3         | $1.6~\mathrm{M}\Omega$ | 9.91 aF     |

| 2         | backplane | 16.3 kΩ                | 970 aF      |

| 2         | 3         | 113 kΩ                 | 139 aF      |

| 3         | backplane | 11.4 kΩ                | 1.38 fF     |

Table 1. Resistance and capacitance values for dynamic model for a three contact example.

# 4. Validity Spectrum of Dynamic Models

In this section the significance of RC models is shown and its limitations evaluated.

# **RC** Model Significance

In order to evaluate the importance and need to account for capacitive coupling through the substrate, the 3D model of Figure 3-b) is taken as example. In particular, looking at any branch in the 3D model and assuming that the capacitive part becomes relevant when the susceptance reaches 10% of the conductance, then:

$$\omega C_{ij} \ge 0.1 G_{ij} \Leftrightarrow \omega \varepsilon \frac{S_{ij}}{l_{ij}} \ge 0.1 \sigma \frac{S_{ij}}{l_{ij}} \Leftrightarrow \omega \ge 0.1 \frac{\sigma}{\epsilon}.$$

(15)

Applying this result to a technology of a single layer substrate with a resistivity  $\rho=\sigma^{-1}=15~\Omega\,cm$  and  $\varepsilon_r=\frac{\varepsilon}{\varepsilon_0}=11.9$ , the previous equation leads to  $\omega=6.33~Grad/s$  which corresponds to approximately 1 gigahertz. This confirms the usual assumption about the validity of resistive models for frequencies up to a few gigahertz, depending on the technology.

Table 1 lists values extracted using the method proposed for a simple configuration such as shown in Figure 4. Using, for instance, computed values of  $R_{10}$  and  $C_{10}$ , and assuming the same error factor of 10%, leads to:

$$\omega C_{10} \ge 0.1 G_{10} \Leftrightarrow \omega \ge 6.33 Grad/s \Leftrightarrow f \approx 1 GHz.$$

(16)

This result, at the contact-level, using extracted data, is compatible with the result at the 3D model mesh level, as expected. It serves as additional validation for the extracted model values. Clearly for frequencies upwards of a few gigahertz, a purely resistive model will be inaccurate as it will not take into account the increase in admittance due to the susceptance term.

# **RC Model Accuracy**

As seen in the previous section, for frequencies greater than a few gigahertz, it becomes necessary to use dynamic coupling models. The model proposed in this paper attempts to fulfill that need and it is necessary to verify its accuracy and limitations.

To simplify the description, and without loss of generality, consider the three contact system from Figure 4 for which we want to compute the admittance description using the method described previously. The input of this system is a vector with the voltages imposed at the contacts,  $[U_1, U_2, U_3]$ . In the extraction methodology proposed, after discretization, a system such as (11) is obtained. Setting a contact's voltage to some value is equivalent to setting the voltages of all nodes in the mesh that fall within the contact to that value. In our case this can be written as  $V = M[U_1, U_2, U_3]^T$ , with  $M \in \Re^{n \times 3}$  an appropriate contact incidence matrix. As nodal analysis is used, the inputs to (11) should be currents, applied to nodes adjacent to the contact nodes. The values of such currents can easily be obtained from the corresponding Norton equivalent circuits seen by those nodes. The complete transformation can be written as:

$$I = Y_{adj} \begin{bmatrix} U_1 \\ U_2 \\ U_3 \end{bmatrix}$$

(17)

where I is the vector of injected currents on all nodes of the 3D mesh and  $Y_{adj} \in \mathbb{C}^{n \times 3}$  is a matrix, combining the incidence matrix M mentioned above and the Norton equivalent admittances seen by the nodes in the mesh. Clearly, most of the entries in  $Y_{adj}$  are zero, with the exception of lines related to the nodes adjacent to the contacts.

On the other hand, the output of the system is given by the current on the destination contact,  $[J_1, J_2, J_3]$ . Combining (11) with (17), it is easy to see that these can be obtained as:

$$\begin{bmatrix} J_1 \\ J_2 \\ J_3 \end{bmatrix} = Y_{adj}^T V = \underbrace{Y_{adj}^T (G + sC)^{-1} Y_{adj}}_{Y_C(s)} \begin{bmatrix} U_1 \\ U_2 \\ U_3 \end{bmatrix}$$

(18)

which exposes the admittance of our simplified three contact system. Obviously this derivation extends trivially to the generic m contacts case.

Several experiments have been elaborated using typical typical substrate profiles, like the ones presented in Figure 5. Properties of the system (18), like pole and zero location, pole residues, Bode plots, etc., were studied. We have come to the conclusion that in single layer isotropic substrates the system behaves approximately like having a single admittance zero. This is due

Figure 5. Typical substrate profiles.

to the 3D system having all poles and zeros clustered around a specific frequency, corresponding to the single intrinsic time-constant of the system, given by  $\sigma/\varepsilon$ . In multiple layer substrates, each layer possesses a different intrinsic time-constant. However, it turns out that a very similar behavior still occurs. For higher frequencies, more dynamic features are exhibited, but for lower frequencies one can see the effect of a dominant admittance "corner" frequency which is now determined by the properties of the top layers where the contacts are contained.

When the frequency  $\omega$  of the least conductive of those layers, layer k, is such that  $\omega > \sigma_k/\epsilon$ , its intrinsic admittance starts to increase, turning into a very low impedance path between contacts, and eventually dominating the overall admittance.

This does not mean system's admittance immediately increases, for the conductance of that particular layer might still be smaller than that of other layers from where contact currents can flow, but eventually it starts to dominate as the path impedance decreases.

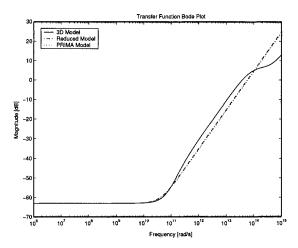

Since we now know that there is a dominant pole/zero behavior, we also computed a first-order PRIMA [Odabasioglu et al., 1998] approximation to the system's behavior. In Figure 6 the Bode diagrams of the full 3D model, the reduced order model and the PRIMA approximation are presented. These plots correspond to the admittance between two contacts for the three-layer substrate profile.

Here, the reduced model parameters were obtained by solving Equation (11) twice: once for  $\omega=0$  rad/s (DC) in order to obtain the resistive component of the coupling,  $G_c$ , and the second time for  $\omega=\sigma_2/\varepsilon=9.491\times 10^{11}$  rad/s (corresponding to the intrinsic cutoff frequency of the middle layer) in order to obtain the capacitive component of the coupling,  $C_c$  (contacts were assumed to have a depth of 4  $\mu$ m). Using just one solve would lead to large coupling estimation errors either at DC or high frequencies. The complete model is obtained by adding  $G_c$  with  $C_c$  like in Equation (12).

Figure 6. Magnitude Bode diagram of 3D transfer function, proposed model and PRIMA model.

As can be seen from the plots, the proposed reduced model and the PRIMA approximation are indistinguishable and have in fact quite similar accuracy. Both of them present a good approximation to the 3D model, accurately capturing the dynamics around the dominant pole/zero and boosting an error smaller than 5 dB for frequencies up to a few hundred gigahertz. Furthermore, the plot also shows quite effectively the limits of using a purely resistive model for substrate coupling.

## **RC Model Simulation**

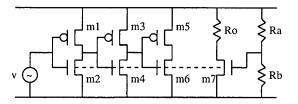

In order to assert for the significance of RC substrate models in circuit simulation, a simple experimental configuration was designed (cf. Figure 7) and simulated. Three CMOS inverters were implanted next to each other and an analog NMOS transistor  $(m_7)$  built near them. A substrate coupling model between all contacts has been extracted. In the simulation phase, the chain of inverters was driven by a 10 GHz sinusoidal wave and the noise injected through the inverters' NMOS diffusion and channel areas was coupled to the sensitive  $m_7$  bulk.

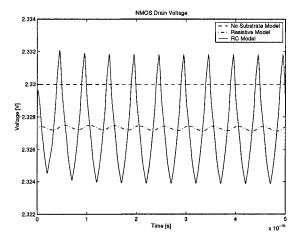

The sensitive transistor has been biased in a way that its drain voltage is constant and equal to 2.33 V in perfect isolation conditions. Figure 8 shows the analog transistor drain voltage in three different situations: when using no substrate coupling model, when using purely resistive coupling models between noise generators and the sensitive transistor, and when using RC coupling models. From the figure, it becomes immediately apparent that the injection of

Figure 7. Simulation test circuit.

Figure 8. Substrate coupling simulation results.

noise into the substrate by the inverters induces substrate voltage fluctuation. Through the body effect of transistor  $m_7$  its drain voltage also bounces instead of being steady as expected with substrate coupling. The difference from resistive to RC models is that resistive models do not account for substrate intrinsic capacitance properties, which at higher frequencies enhance coupling effects. Resistive models are therefore unable to predict correct functioning of the analog transistor in this case.

Clearly, this example demonstrates the need for substrate RC dynamic models for frequencies higher that a few gigahertz and it also validates the accuracy of the proposed method for frequencies up to several tens of gigahertz.

## 5. Conclusions

A methodology for the extraction of dynamic RC substrate coupling models, that naturally extends the traditional resistive-only modeling techniques,

has been presented. Reduced models obtained for a formulation based on Finite Difference discretization were computed using a fast Multigrid algorithm and are shown to offer high accuracy for a large spectrum of frequencies. Further studies also showed that a first order approximation computed with standard model order reduction techniques will offer similar accuracy at similar computational cost.

Extensive experiments and simulations of a simple example circuit performed using the proposed model demonstrate both its relevance and accuracy for frequencies up to several tens of gigahertz.

# 6. Acknowledgment

This work was partially supported by a scholarship from the Portuguese Foundation for Science and Technology under the POSI program.

We would like to thank Dr. Edgar Albuquerque for his helpful hints on model simulation and substrate noise analysis.

#### References

- Chou, Mike and White, Jacob (1998). Multilevel integral equation methods for the extraction of substrate coupling parameters in mixed-signal ic's. In 35<sup>th</sup> ACM/IEEE Design Automation Conference, pages 20–25.

- Clement, F. J. R., Kayal, E. Zysman M., and Declercq, M. (1994). Layin: Toward a global solution for parasitic coupling modeling and visualization. In *Proc. IEEE Custom Integrated* Circuit Conference, pages 537-540.

- Costa, Joao P., Chou, Mike, and Silveira, L. Miguel (1998). Efficient techniques for accurate modeling and simulation of substrate coupling in mixed-signal IC's. In *DATE'98 Design*, Automation and Test in Europe, Exhibition and Conference, pages 892–898, Paris, France.

- Feldmann, P. and Freund, R. W. (1995). Efficient linear circuit analysis by Pade approximation via the Lanczos process. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 14(5):639-649.

- Gharpurey, R. and Meyer, R. G. (1995). Modeling and analysis of substrate coupling in integrated circuits. In *IEEE 1995 Custom Integrated Circuits Conference*, pages 125–128.

- Gharpurey, Ranjit (1995). Modeling and Analysis of Substrate Coupling in Integrated Circuits. PhD thesis, Department of Electrical Engineering and Computer Science, University of California at Berkeley, Berkeley, CA.

- Gharpurey, Ranjit and Hosur, Srinath (1997). Transform domain techniques for efficient extraction of substrate parasitics. In *Proceedings of the Int. Conf. on Computer-Aided Design*, pages 461–467.

- Joardar, Kuntal (1994). A simple approach to modeling cross-talk in integrated circuits. IEEE Journal of Solid-State Circuits, 29(10):1212–1219.

- Johnson, T. A., Knepper, R.W., Marcellu, V., and Wang, W. (1984). Chip substrate resistance modeling technique for integrated circuit design. *IEEE Transactions on Computer-Aided Design of Integrated Circuits*, CAD-3(2):126-134.

- Kanapka, J., Phillips, J., and White, J. (2000). Fast methods for extraction and sparsification of substrate coupling. In Proc. 37th Design Automation Conference.

- Kup, B.M.J., Dijkmans, E.C., Naus, P.J.A., and Sneep, J. (1991). A bit-stream digital-to-analog converter with 18-b resolution. *IEEE Journal of Solid-State Circuits*, 26(12):1757–1763.

- Mitra, Sujoy, Rutenbar, R. A., Carley, L. R., and Allstot, D. J. (1995). A methodology for rapid estimation of substrate-coupled switching noise. In *IEEE 1995 Custom Integrated Circuits Conference*, pages 129–132.

- Nauta, Bram and Hoogzaad, Gian (1997). How to deal with substrate noise in analog CMOS circuits. In European Conference on Circuit Theory and Design, pages Late 12:1–6, Budapest, Hungary.

- Odabasioglu, A., Celik, M., and Pileggi, L. T. (1998). PRIMA: passive reduced-order interconnect macromodeling algorithm. *IEEE Trans. Computer-Aided Design*, 17(8):645–654.

- Phillips, Joel R and Silveira, L. Miguel (2001). Simulation approaches for strongly coupled interconnect systems. In *International Conference on Computer Aided-Design*.

- Silva, Jono M. S. (2003). Modeling substrate coupling in mixed analog-digital circuits (in portuguese). Master's thesis, Instituto Superior Tecnico, Technical University of Lisbon, Lisboa, Portugal.

- Silveira, L. Miguel, Kamon, Mattan, and White, Jacob K. (1995). Algorithms for Coupled Transient Simulation of Circuits and Complicated 3-D Packaging. IEEE Transactions on Components, Packaging, and Manufacturing Technology, Part B: Advanced Packaging, 18(1):92–98.

- Silveira, L. Miguel and Vargas, Nuno (2002). Characterizing substrate coupling in deep submicron designs. *IEEE Design & Test of Computers*, 19(2):4–15.

- Smedes, T., van der Meijs, N. P., and van Genderen, A. J. (1995). Extraction of circuit models for substrate cross-talk. In *International Conference on Computer Aided-Design*, San Jose, CA.

- Stanisic, Balsha, Verghese, Nishath K., Rutenbar, Rob A., Carley, L. Richard, and Allstot, David J. (1994). Addressing substrate coupling in mixed-mode IC's: Simulation and power distribution systems. *IEEE Journal of Solid-State Circuits*, 29(3):226–237.

- Su, David K., Loinaz, Marc J., Masui, Shoichi, and Wooley, Bruce A. (1993). Experimental results and modeling techniques for substrate noise in mixed-signal integrated circuits. *IEEE Journal of Solid-State Circuits*, 28(4):420–430.

- van Genderen, A. J., van der Meijs, N. P., and Smedes, T. (1996). Fast computation of substrate resistances in large circuit. In *European Design and Test Conference*, Paris.

- Verghese, Nishath (1995). Extraction and Simulation Techniques for Substrate-Coupled Noise in Mixed-Signal Integrated Circuits. PhD thesis, Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA.

- Verghese, Nishath K. and Allstot, David J. (1995). Subtract: A program for the efficient evaluation of substrate parasitics in integrated circuits. In *International Conference on Computer Aided-Design*, San Jose, CA.

- Wemple, Ivan L. and Yang, Andrew T. (1995). Mixed-signal switching noise analysis using voronoi-tesselation substrate macromodels. In 32<sup>nd</sup> ACM/IEEE Design Automation Conference, pages 439–444, San Francisco, CA.