Paul Molitor und Jörg Ritter

# **VHDL**

Eine Einführung

ein Imprint von Pearson Education

München • Boston • San Francisco • Harlow, England Don Mills, Ontario • Sydney • Mexico City Madrid • Amsterdam

#### **Kapitel**

## Aufbau und Grundkonzepte von VHDL

Dieses Kapitel stellt die in VHDL verfügbaren Konstrukte, Datentypen, Attribute und Kontrollstrukturen vor. Ähnliche Kapitel findet man in der Regel in jedem Lehrbuch zu einer Programmiersprache, die alle — wie auch in diesem Buch — mehr oder weniger langweilig zu lesen sind. Nichtsdestotrotz sollten Sie diesem Kapitel Beachtung schenken, da VHDL doch einige Konzepte zur Verfügung stellt, die in "üblichen" Programmiersprachen nicht vorzufinden sind. Später können Sie dieses Kapitel wie ein Nachschlagewerk benutzen.

Wir geben keine vollständige Übersicht in dem Sinne, dass wirklich alle in VHDL zur Verfügung gestellten Elemente hier aufgezählt und erläutert sind. Wir haben uns aber bemüht, die wichtigsten, sprich die am häufigsten benutzten Konzepte hier anzusprechen. Sollten "ein oder zwei" fehlen, so bitten wir dies zu entschuldigen und verweisen für diesen Fall auf das fast 700-seitige Standardwerk von Ashenden [3].

Wir waren in diesem Kapitel auch gezwungen, zum Teil auf noch nicht eingeführte Elemente von VHDL vorzugreifen, um die vorgestellten VHDL-Elemente an sinnvollen Beispielen illustrieren zu können.

## 3.1 Genereller Aufbau einer VHDL-Spezifikation

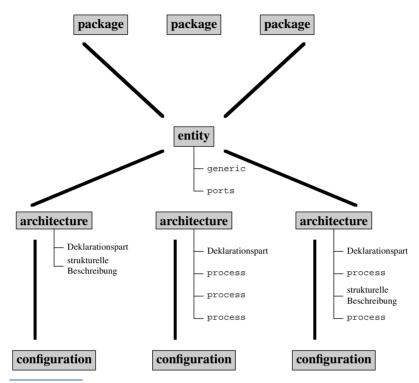

Abbildung 3.1 zeigt den prinzipiellen Aufbau einer VHDL-Beschreibung, die aus einem Entity und einer oder mehreren Architekturen — im Regelfall einer Architektur — besteht. Packages, wie zum Beispiel die von IEEE vorgegebenen Packages std\_logic\_1164 und std\_logic\_textio, auf die wir im Kapitel 5 detailliert eingehen werden, können eingebunden werden. Sie stellen oft benutzte Konstanten, Datentypen, Funktionen und Prozeduren zu Verfügung.

Da wir den Funktionen und Prozeduren als auch den Packages spezielle Kapitel in diesem Buch gewidmet haben (siehe Kapitel 4 und Kapitel 5), wollen wir an dieser Stelle nicht auf diese eingehen und uns auf die restlichen Konstrukte konzentrieren.

Abbildung 3.1: Aufbau einer VHDL-Beschreibung

#### 3.1.1 Schnittstellen-Beschreibung eines Bausteins

Lassen Sie uns mit dem **entity**-Konstrukt beginnen. Wie Abbildung 3.1 zeigt, enthält die Beschreibung eines jeden mit VHDL beschriebenen Bausteins (beziehungsweise Schaltkreises) eine solche **entity**. Eine Entity ist in der Regel wie folgt aufgebaut:

```

entity Name_des_Bausteins is

[ generic ( Parameter_Liste ); ]]

[ port ( Liste_der_Ein_und_Ausgabepins ); ]]

end [ entity ]] [ Name_des_Bausteins ]];

```

Die Entity eines Bausteins legt dessen Namen fest und beschreibt seine Schnittstelle zur Außenwelt.<sup>1</sup> Die Schnittstelle wird im Wesentlichen durch die Ports beschrieben, die festlegen, welche Eingabe- und Ausgabesignale der Baustein hat. Diese Schnittstelle

Die in [ und ] eingeschlossenen Zeichenketten sind optional und sind nur bei Bedarf Bestandteil des Konstrukts. Wie Sie feststellen werden, verwenden wir in diesem Kapitel zum Teil eine recht informale Schreibweise, um Ihnen die Syntax nahe zu bringen. Die exakte Syntax – exakt auch in Bezug auf die Schreibweise – ist in Kapitel 11 zu finden.

kann über generische Parameter parametrisiert sein. Zur Illustration sei hier bereits auf das Kapitel 6 vorgegriffen, in dem der mit der Wortbreite der Operanden parametrisierte serielle und der so genannte log *n*-Addierer/Subtrahierer mit VHDL beschrieben werden. Deren Schnittstelle könnte zum Beispiel durch

```

3    entity add_sub is

4        generic (n: positive);

5        port

6          (a, b: in std_logic_vector (n-1 downto 0);

7          op: in std_logic;

8          s: out std_logic_vector (n-1 downto 0);

9          ov: out std_logic);

10    end add sub:

```

gegeben sein. Der Baustein bekommt mit dieser Entity-Beschreibung den Namen add\_sub zugeordnet. Die Ports sind mit dem generischen Parameter n, der über den Datentyp positive deklariert ist, parametrisiert. Der Baustein besitzt drei Eingabeports, von denen zwei, nämlich die Ports a und b, jeweils einen Vektor über dem Datentyp std\_logic der Länge n darstellen. Von den beiden Ausgabeports ist Port s ebenfalls ein Vektor der Länge n.

Bei den Ports unterscheidet VHDL zwischen Eingabeports, Ausgabeports und so genannten bidirektionalen Ports.<sup>2</sup> Die entsprechende Zuordnung eines Ports erfolgt in der Port-Deklaration über das Schlüsselwort **in, out** oder **inout**.

#### Fallstrick 3

Ist ein Port als **in**-Port deklariert, so kann nur lesend auf diesen Port durch den Baustein zugegriffen werden; ist er als **out**-Port deklariert, so ist nur schreibender Zugriff möglich.

Ports vom Modus **inout** stellen Ports dar, die, je nach Kontext beziehungsweise abwechselnd, als Eingabeports oder Ausgabeports fungieren. Bei Benutzung von **inout**-Ports muss auf die Synthetisierbarkeit des Entwurfs Acht gegeben werden. Ein Beispiel, wie bidirektionale Ports modelliert werden können, sodass diese Beschreibungen auch synthetisierbar sind, finden Sie im Abschnitt 9.2.

Nicht jeder Baustein ist generischer Art, sodass der generische Parameter im **entity**-Konstrukt optional ist. Beispiele nicht generischer Bausteine sind das Flipflop und das Schieberegister der Breite 4, deren Schnittstellen-Beschreibungen durch

Neben diesen drei Modi stellt VHDL noch die Modi buffer und linkage zur Verfügung. Ein buffer-Port ist ein out-Port, auf den der Baustein auch lesend zugreifen kann. Buffer-Ports haben kein Äquivalent in wirklicher Hardware. Der Modus linkage dient dazu, um in VHDL spezifizierte Bausteine mit nicht in VHDL spezifizierten Bausteinen kombinieren zu können. Beide Modi finden nur selten Anwendung.

```

4

entity flipflop is

5

port ( clockpin, resetpin, data_in: in std_logic;

data out: out std logic ):

6

7

end flipflop;

und

4

entity schieberegister 4 is

5

port ( clockpin, resetpin, data in : in std logic;

6

data out : out std logic );

7

end schieberegister 4:

```

angegeben werden können. Beide Bausteine werden wir noch im Rahmen der folgenden Abschnitte benötigen

Im Rahmen einer Schnittstellen-Beschreibung können des Weiteren Eingabeports für den Fall auf einen Default-Wert gesetzt werden, dass ein Eingabeport (oder mehrere) bei Verwendung des Bausteins als Komponente eines anderen Bausteins nicht durch ein Signal getrieben werden würde. Zur Illustration sehen wir uns nochmals das oben angegebene Entity des kombinierten Addierer/Subtrahierer an. Über den Eingabeport op wird die Art der Operation gewählt. Liegt am Eingabeport der Wert '0' an, so sollen die beiden Operanden a und b addiert werden, liegt der Wert '1' an, so soll der Operand b von dem Operanden a subtrahiert werden. VHDL bietet nun die Möglichkeit, schon in der entity-Deklaration zu spezifizieren, dass standardmäßig zum Beispiel addiert werden soll, wenn der Eingabeport ov offen bleibt — dies erfolgt dadurch, dass diesem Eingabeport während der Instanziierung der Komponente "das Schlüsselwort open zugewiesen" wird. Die erweiterte Schnittstellen-Beschreibung hat dann das Aussehen

```

3a

entity add_sub is

3b

generic (n: positive);

3c

port

3d

(a, b: in std_logic_vector (n-1 downto 0);

3e

op : in std logic:='0';

s : out std_logic_vector (n-1 downto 0);

3 f

ov : out std_logic);

3g

3h

end add sub:

```

#### Fallstrick 4

Alle Default-Belegungen werden bei der Synthese ignoriert. Die vorbelegten Ports müssen explizit verbunden werden. Eine Initialisierung von Signalen und Variablen muss über ein asynchrones oder synchrones Reset erfolgen!

Es sei auch darauf hingewiesen, dass die Angabe der Ports selbst optional ist, d. h. eine Entity der Art

```

4 entity test is

5 end test;

```

ist erlaubt und wird in der Tat auch im Rahmen der Implementierung von Testbenches benutzt. Testbenches, auf die wir detailliert im Teil IV noch zu sprechen kommen, könnten beispielsweise Stimuli und das dazugehörige Soll-Verhalten eines zu validierenden Bausteins aus einer Datei einlesen, diese Stimuli an den Baustein anlegen und das Ist-Verhalten mit dem Soll-Verhalten vergleichen. Die Ergebnisse der Vergleiche könnten wieder in eine Datei gespeichert werden oder mit **report**-Anweisungen auf die Standardausgabe ausgegeben werden. Insofern ist eine solche Testbench formal gesehen ein Baustein ohne Eingabe- und Ausgabeport.

Zuletzt sei noch bemerkt, dass Entities "Plausibilitätskontrollen", so genannte nebenläufige **assert**-Anweisungen, auf die wir im Abschnitt 3.5 noch detailliert eingehen werden, enthalten können, sodass eine allgemeinere Form der Beschreibung von Entities wie folgt<sup>3</sup>

```

entity Name_des_Bausteins is

[ generic ( Parameter_Liste ); ]]

[ port ( Liste_der_Ein_und_Ausgabepins ); ]]

[ begin

{ nebenläufige_assert_Anweisung } ]]

end [[ entity ]] [[ Name_des_Bausteins ]];

```

aussieht. Beispielsweise deklariert

```

4

entity single2double is

5

-- Baustein zur Konvertierung

6

-- einer n-bit Zweierkomplement-Darstellung

-- in eine m-bit Zweierkomplement-Darstellung mit n<=m</p>

7

8

port (

9

inp: in std_logic_vector;

10

outp: out std_logic_vector);

11

begin

12

ueberpruefe_laenge:

assert inp'length <= outp'length</pre>

13

14

report "Die Wortbreite des Ausgangs ist zu klein!";

15

16

ueberpruefe rechter index:

17

assert inp'right = 0 and outp'right = 0

18

report "Rechte Komponente muss Index 0 haben!";

19

end entity single2double;

```

einen Baustein, der eine n-Bit-Zweierkomplement-Darstellung in eine m-Bit Zweierkomplement-Darstellung umwandelt. Beachten Sie bitte, dass es sich bei den Ports um

Die in geschweiften Klammern eingeschlossenen Zeichenketten k\u00f6nnen beliebig oft hintereinander eingesetzt werden. N\u00e4here Informationen zu den Schreibweisen sind in Abschnitt 11.1 auf Seite 255 zu finden.

unbeschränkte Felder (siehe Abschnitt 3.3.2 auf Seite 90) handelt. Aus diesem Grunde muss überprüft werden — diese Überprüfung erfolgt über die erste **assert**-Anweisung —, ob die Wortbreite m des Ausgangssignals outp, die über das Attribut outp'length abgefragt werden kann, breiter als die Wortbreite n (= inp'length) ist — ansonsten ist die durch den Baustein zu realisierende Operation unsinnig. Zudem sollte die rechte Komponente des übergebenen Signals jeweils den Index 0 haben.

#### 3.1.2 Architekturen eines Bausteins

Lassen Sie uns jetzt zum VHDL-Konstrukt **architecture** kommen, welches das Herzstück einer VHDL-Beschreibung eines Bausteins bildet. Während das **entity**-Konstrukt das Interface, d. h. die Ein- und Ausgabeschnittstelle, eines Bausteins beschreibt, gibt das **architecture**-Konstrukt die Realisierung des Bausteins an.

Eine Architektur ist in der Regel wie folgt aufgebaut:

```

architecture Name_der_Architektur of Name_des_Bausteins is

[ Deklarationsteil ]]

begin

{ VHDL-Anweisung }

end Name_der_Architektur;

```

So spezifiziert der Quellcode<sup>4</sup>

```

9

architecture D_flipflop of flipflop is

10

begin

11

VERHALTEN: process(clockpin,resetpin)

12

begin

13

if resetpin='1' then

data_out <= '0';</pre>

14

15

elsif rising_edge(clockpin) then

16

data_out <= data_in;</pre>

17

end if:

18

end process;

end D_flipflop;

```

eine funktionale Beschreibung des Bausteins flipflop, dessen Interface in der schon oben angegebenen **entity**-Anweisung spezifiziert wurde. Die Architektur besteht aus einem Prozess namens VERHALTEN, der immer dann aktiviert wird, wenn eine Signaländerung auf der Taktleitung oder der Reset-Leitung, die durch das Signal clockpin beziehungsweise das Signal resetpin modelliert werden, erfolgt ist. Der Prozess beschreibt in Abhängigkeit der Belegung des Signals resetpin das Signal data\_out. Ist die Reset-Taste gedrückt, d. h. gilt reset\_pin=1, so wird das Signal data\_out auf den

<sup>4</sup> Das Konstrukt rising\_edge(clk) entspricht der Abfrage auf die steigenden Flanke der Taktleitung (clk='1' and clk'event).

Wert '0' zurückgesetzt. Ansonsten übernimmt es den Wert des Signals data\_in bei steigender Flanke am Takteingang.

Wir wollen an dieser Stelle auch schon darauf hinweisen, dass zu einer Entity nicht nur eine Architektur angegeben werden darf, sondern auch mehrere Architekturen angegeben werden können. So könnte man sich überlegen, das Flipflop auch nach dem Master-Slave-Prinzip aufzubauen, was in der Architektur

```

architecture master slave of flipflop is

2.1

22

signal zustand des masters: std logic;

23

begin

24

MASTER: process(clockpin,resetpin)

25

begin

26

if resetpin='1' then

27

zustand des masters <= '0';</pre>

28

elsif rising_edge(clockpin) then

29

zustand_des_masters <= data_in;</pre>

30

end if:

31

end process:

32

SLAVE: process(clockpin,resetpin)

33

begin

34

if resetpin='1' then

35

data out <= '0':

36

elsif falling edge(clockpin) then

37

data_out <= zustand_des_masters;</pre>

38

end if:

39

end process:

40 end master_slave;

```

die im Wesentlichen aus zwei nebenläufigen Prozessen besteht, resultieren würde. Wird der flipflop-Baustein dann als Komponente in einer strukturellen Beschreibung eines anderen Schaltkreises verwendet, so wird über eine **configuration**-Anweisung für jeden der Instanzen angegeben, welche Architektur zu verwenden ist. Wir werden auf diesen Punkt in Abschnitt 3.1.3 im Detail zu sprechen kommen.

#### **Funktionale Beschreibungen**

Die beiden oben angegebenen Architekturen D-flipflop und master\_slave des Bausteins flipflop wurden mit Hilfe funktionaler Beschreibungen spezifiziert.

Funktionale Beschreibungen bestehen aus einer Menge von nebenläufigen (expliziten und impliziten) Prozessen.

Die Syntax eines Prozesses ist durch

```

[ Marke : ] process [ ( Sensitivitätsliste ) ] [ is ]

Deklarationsteil

begin

Ausführungsteil

end [ process ] [ Marke ] ;

```

gegeben.

Im Deklarationsteil eines Prozesses können Datentypen, Funktionen und Prozeduren definiert und Variablen sowie Konstanten deklariert werden.

#### Fallstrick 5

Signale können nicht in Prozessen, sondern nur im Deklarationsteil einer Architektur beziehungsweise im Port-Deklarationsteil einer Entity-Beschreibung deklariert werden.

Der Ausführungsteil eines Prozesses besteht aus einer Folge von sequentiellen Anweisungen, die wie der Name schon sagt, sequentiell nacheinander durch die Simulation ausgeführt werden.

Mehr zu Prozessen ist in Kapitel 2 im Abschnitt 2.2.3, der sich mit der Ausführung von Prozessen während eines Simulationslaufes beschäftigt, ab Seite 55 zu finden.

#### Strukturelle Beschreibungen

Neben funktionalen Beschreibungen erlaubt VHDL auch strukturelle Beschreibungen. Zur weiteren Illustration lassen Sie uns verschiedene Architekturen des 4-Bit-Schieberegisters angeben, dessen Schnittstellen-Beschreibung wir oben schon angegeben haben. Hiermit wollen wir, auch schon im Vorgriff auf die nächsten Abschnitte, zeigen, welche Möglichkeiten VHDL uns zur Realisierung von Architekturen zur Verfügung stellt.

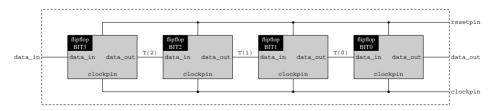

Abbildung 3.2: Aufbau eines 4-Bit-Schieberegisters

Abbildung 3.3 zeigt den VHDL-Quellcode des in Abbildung 3.2 gezeigten Aufbaus des Schieberegisters. Die Architektur haben wir RTL1 genannt — die Abkürzung kommt von

```

9

architecture RTL1 of schieberegister 4 is

10

component flipflop

port ( clockpin, resetpin, data_in: in std_logic;

11

12

data out: out std logic );

end component:

13

14

signal T: std_logic_vector(2 downto 0);

15 begin

16

BIT3 : flipflop

17

port map ( clockpin => clockpin, resetpin => resetpin,

18

data in \Rightarrow data in, data out \Rightarrow T(2));

19

BIT2: flipflop

20

port map ( clockpin => clockpin, resetpin => resetpin,

21

data_in \Rightarrow T(2), data_out \Rightarrow T(1);

22

BIT1: flipflop

23

port map ( clockpin, resetpin, T(1), T(0) );

24

BITO: flipflop

25

port map ( data_in => T(0), data_out => data_out,

26

resetpin => resetpin, clockpin => clockpin );

27 end RTL1:

```

Abbildung 3.3: Eine erste strukturelle Architektur des Bausteins schieberegister 4

der englischen Bezeichnung *Register Transfer Level*, die eine im Rahmen der Hardwarebeschreibung oft verwendete Abstraktionsebene bezeichnet.

Hier sehen wir etwas detaillierter, wie in der Regel eine Architektur, die auf einer strukturellen Beschreibung basiert, aussieht.

■ Im Deklarationsteil werden neben notwendigen internen Signalen alle Komponenten, die zur strukturellen Beschreibung benötigt werden, über das Schlüsselwort **component** deklariert. In unserem Beispiel — betrachten Sie den Aufbau in Abbildung 3.2 — sind dies die Komponente flipflop und die internen, durch das Feld T modellierten, Signale, welche die einzelnen Instanzen dieser Komponente miteinander verbinden.

Eine Komponenten-Deklaration sieht formal wie folgt aus:

```

component Name_des_Bausteins is

[ generic ( Parameter_Liste ); ]]

[ port ( Liste_der_Ein_und_Ausgabepins ); ]]

end component;

```

Im eigentlichen Beschreibungsblock werden dann nacheinander die vier Instanzen der Komponente flipflop generiert — wir sprechen von der Instanzierung von Komponenten —; sie tragen die Namen BIT3, BIT2, BIT1 und BIT0. Über die **port map**-Anweisung werden jeweils die Ports der Instanzen mit der Außenwelt verdrahtet. Wir erkennen zwei Arten der Port-Verdrahtung, das so genannte *name mapping* und das so genannte *positional mapping*.

- Name mapping haben wir in unserem Beispiel bei der Instanziierung von BIT3, BIT2 und BIT0 angewendet. Hier erfolgt die Verdrahtung direkt über die Portnamen. Die Reihenfolge, in der dies erfolgt, ist egal. Beispielsweise haben wir die Reihenfolgen bei den Instanziierungen von BIT2 und BIT0 unterschiedlich gewählt.

- Bei Positional Mapping erfolgt die Port-Verdrahtung, wie in vielen Programmiersprachen üblich, über die Position der Ports und der Signale hier steckt also die Information, wer mit wem, in der Reihenfolge, in der die "aktuellen Parameter" übergeben werden. Ein Beispiel ist bei der Instanziierung von BIT1 zu sehen.

Instanziierungen von Komponenten haben allgemein das Aussehen

```

Instanziierung_Marke: Name_der_Komponente

[generic map ( Zuweisung_an_die_generischen_Parameter ); ]

[port map ( Anbindung_der_Ein_und_Ausgabepins ); ]]

```

Der in Abbildung 3.3 angegebene Quellcode wirkt beschwerlich, wenn man Schieberegister größerer Breite spezifizieren möchte, da man für jede benötigte Instanz der Komponente flipflop explizit eine Instanziierung-Anweisung angeben muss.

Um hier Abhilfe zu schaffen, stellt VHDL die Anweisungen **for...generate** und **if...generate** zur Verfügung. Abbildung 3.4 zeigt eine strukturelle Beschreibung unseres 4-Bit Schieberegisters, die diese Anweisungen verwendet. Man sieht leicht, dass entsprechend größere Schieberegister nun mit dem gleichen Aufwand beschrieben werden können wie das Schieberegister der Breite 4. Wir werden gleich nochmals hierauf zurückkommen.

In dem Quellcode in Abbildung 3.4 sind vier **generate**-Anweisungen enthalten. Eine **for...generate**-Anweisung und drei **if...generate**-Anweisungen. Die **for...generate**-Anweisung ermöglicht die iterative Instanziierung einer Komponente. So werden hier vier Instanziierungen der Komponente flipflop vorgenommen. Die Port-Verdrahtung der Instanzen wird über die **if...generate**-Anweisungen gesteuert. Ist die Laufvariable i — sie muss nicht (und darf auch nicht) deklariert werden; sie ist zudem nur innerhalb der **for**-Schleife gültig —, gleich 0, so soll die hintere Instanz des Schieberegisters generiert werden; ist die Laufvariable i gleich 3, so soll die vordere Instanz generiert werden, ansonsten handelt es sich um eine Instanz, die über die Signal T(i) und T(i-1) mit ihrer Umgebung verbunden ist.

Einer **generate**-Anweisung muss wie einer Instanziierung einer Komponente eine Marke voranstehen — dies sind in unserem Beispiel die Marken G0, G1, G2 und G3. Diese Marken schaffen die Voraussetzung, die verschiedenen Instanzen einer Komponente an unterschiedliche Architekturen des zugehörigen Entity binden zu

können. Nähere Informationen zu diesem Themenkreis sind im Abschnitt 3.1.3 zu finden. Während der Simulation kann über die Marken die jeweilige Instanz ausgewählt werden. In diesem Kontext wirken die Marken wie ein Selektor innerhalb der Schaltungshierarchie.

```

29

architecture RTL2 of schieberegister 4 is

30

component flipflop

31

port ( clockpin, resetpin, data_in: in std_logic;

32

data_out: out std_logic );

33

end component;

34

signal T: std_logic_vector(2 downto 0);

35

begin

36

GO: for i in 3 downto 0 generate

37

G1: if (i = 3) generate

38

BIT3: flipflop

39

port map (clockpin,resetpin,data_in,T(2));

40

end generate:

41

G2: if (i>0) and (i<3) generate

42

BITm: flipflop

43

port map (clockpin,resetpin,T(i),T(i-1));

44

end generate;

45

G3: if (i=0) generate

46

BITO: flipflop

47

port map (clockpin,resetpin,T(0),data_out);

48

end generate:

49

end generate:

50 end RTL2;

```

Abbildung 3.4: Strukturelle Architektur des Bausteins schieberegister\_4 unter Verwendung der generate-Anweisungen

Die **for...generate**- und **if...generate**-Anweisungen sind wesentlich, um generische Bausteine mit VHDL beschreiben zu können. Ein ausführliches Beispiel zu dieser Thematik befindet sich in Kapitel 6.

Zur Einstimmung wollen wir uns aber hier schon ein generisches Schieberegister anschauen. Die Länge des Schieberegisters kann über einen Parameter n den Erfordernissen angepasst werden. Abbildung 3.5 zeigt das Entity und eine dazugehörige Architektur. Wenn wir den Quellcode mit dem aus Abbildung 3.4 vergleichen, sehen wir in der Tat, welche Beschreibungsmöglichkeiten uns mit den **generate**-Anweisungen gegeben sind. Die Architektur ist eine Kopie der in Abbildung 3.4 gegebenen Architektur des 4-Bit-Schieberegisters mit Ausnahme, dass wir anstelle der Konstante 3 nunmehr den generischen Wert n-1 verwenden.

```

4

entity schieberegister is

5

generic ( n : positive ):

port ( clockpin, resetpin, data_in : in std_logic;

6

7

data out : out std logic );

8

end schieberegister;

9

10

architecture RTL of schieberegister is

11

component flipflop

12

port ( clockpin, resetpin, data in: in std logic;

13

data_out: out std_logic );

14

end component:

15

signal T: std logic vector(n-1 downto 0);

16

begin

17

GO: for i in n-1 downto O generate

18

G1: if (i = n-1) generate

19

BIT high: flipflop

20

port map (clockpin,resetpin,data_in,T(n-1));

21

end generate:

22

G2: if (i>0) and (i<n-1) generate

23

BITm: flipflop

24

port map (clockpin,resetpin,T(i),T(i-1));

25

end generate;

G3: if (i=0) generate

26

27

BITO: flipflop

28

port map (clockpin,resetpin,T(0),data_out);

29

end generate;

30

end generate;

31

end RTL:

```

Abbildung 3.5: VHDL-Beschreibung eines generischen Schieberegisters

#### 3.1.3 Konfigurationen

Zu einer Entity können mehrere Architekturen definiert sein. Wir müssen also die Zuordnung zur Schnittstellenbeschreibung festlegen.

Dies erfolgt über so genannte Konfigurationen. Hiermit kann elegant für bestimmte oder auch alle Instanzen einer verwendeten Komponente entschieden werden, welche Realisierung zum Einsatz kommt. Eine Konfiguration sieht in ihrer einfachsten Form wie folgt aus:

So könnten die Konfigurationen unseres 4-Bit-Schieberegisters zum Beispiel durch

```

configuration CFG1a of schieberegister_4 is

52

for RTL1

53

54

for all: flipflop

55

use entity work.flipflop(D_flipflop);

56

end for:

57

end for:

58 end CFG1a:

beziehungsweise

configuration CFG2 of schieberegister_4 is

68

for RTI2

69

70

for GO

71

for G1

72

for BIT3: flipflop

73

use entity work.flipflop(D_flipflop);

74

75

end for:

76

end for:

77

for others: flipflop

use entity work.flipflop(master_slave);

78

79

80

end for:

end CFG2:

81

```

gegeben sein. Wir wollen beide Codefragmente erläutern.

■ Will man die Instanzen einer Komponente einer Architektur alle an die gleiche Architektur der entsprechenden Entity — die Anweisung

```

use entity work.flipflop(D_flipflop);

```

besagt, dass die Architektur D\_flipflop der Entity flipflop, die in der Bibliothek work abgelegt ist, verwendet werden soll — binden, so kann dies, wie oben im ersten Beispiel gezeigt, über eine **for all**-Anweisung, gefolgt von dem entsprechenden **use**-Befehl, erfolgen. Äquivalent dazu, vom Schreibaufwand aber aufwändiger, wäre die Konfiguration

```

60 configuration CFG1b of schieberegister_4 is

61    for RTL1

62    for BIT3, BIT2, BIT1, BIT0: flipflop

63        use entity work.flipflop(D_flipflop);

64    end for;

65    end CFG1b;

```

■ Ein bisschen komplizierter sieht es aus, wenn man verschiedenen Instanzen einer Komponente verschiedene Realisierungen zuordnen will. In diesem Fall sind wir, wie im zweiten Beispiel zu sehen ist, gezwungen, die verschiedenen Instanzen eindeutig zu spezifizieren. Dies erfolgt über den, durch die Marken, die jeder for...generate-

und **if...generate**-Anweisung sowie jeder eigentlichen Instanziierung einer Komponente vorstehen müssen, eindeutig definierten Pfad zu der einzelnen Instanz. So sehen wir in dem obigen zweiten Beispiel, dass der Instanz der Entity flipflop, die über den Pfad  $GO \to GI \to BIT3$  in der Architektur RTL2 erreicht wird, die Architektur  $D_flipflop$  zugewiesen wird. Den übrigen Instanzen der Entity flipflop der Architektur RTL2 wird die Architektur master\_slave der Entity flipflop, die ebenfalls in der Bibliothek work abgespeichert ist, zugewiesen. Hierfür steht die **for others**-Anweisung zur Verfügung.

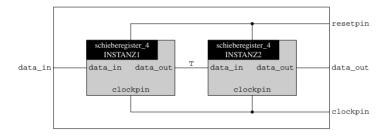

Noch komplizierter wird es, wenn die Hierarchie der (strukturellen) VHDL-Beschreibung tiefer als 1 ist. Wir wollen dies an einem 8-Bit-Schieberegister illustrieren. Schematic, **entity** und **architecture** des Bausteins sind in Abbildung 3.6 zu sehen. In dieser Architektur ist das 8-Bit-Schieberegister aus zwei 4-Bit-Schieberegistern aufgebaut, die, wie wir gesehen haben, selbst wieder über eine strukturelle Beschreibung beschrieben und über Flipflops aufgebaut sind. Die Hierarchie dieser strukturellen Architektur hat in diesem Sinne Tiefe 2.

```

4

entity schieberegister_8 is

5

port ( clockpin, resetpin, data_in : in std_logic;

6

data out : out std logic );

7

end schieberegister_8;

8

9

architecture RTL of schieberegister 8 is

component schieberegister 4

10

port ( clockpin, resetpin, data_in: in std_logic;

11

12

data_out: out std_logic );

13

end component;

14

signal T: std_logic;

15

begin

16

INSTANZ1: schieberegister_4

17

port map (clockpin => clockpin, resetpin=>resetpin,

18

data_in => data_in, data_out => T);

19

INSTANZ2: schieberegister_4

20

port map (clockpin => clockpin, resetpin=>resetpin,

21

data_in => T, data_out => data_out);

22

end RTL;

```

Abbildung 3.6: 8-Bit-Schieberegister aufgebaut aus zwei 4-Bit-Schieberegistern

Hier reicht es nun offensichtlich nicht, in der dazugehörigen Konfiguration anzugeben, welche Architekturen den beiden Instanzen der Komponente schieberegister\_4 zugeordnet werden sollen, da diese Architekturen wiederum Instanzen von Komponenten, in diesem Falle der Komponente flipflop, enthalten, denen ebenfalls wieder Realisierungen zugeordnet werden müssen.

Hier stellt nun VHDL zwei Alternativen zur Verfügung, wobei letztere in unseren Augen zu bevorzugen ist. Wir wollen die beiden Möglichkeiten für den Fall illustrieren, dass den Instanzen der Komponente schieberegister\_4, die in der in Abbildung 3.6 gezeigten Architektur RTL des Bausteins schieberegister\_8 vorkommen, die Architektur RTL2 zugeordnet wird.

■ Als Erstes können wir so vorgehen, dass wir rekursiv den einzelnen Instanzen der Komponenten in der bekannten Art und Weise Architekturen zuordnen. Dies resultiert in einer Konfiguration mit etwa dem folgenden Aussehen.

```

configuration CFG1 of schieberegister 8 is

25

for RTL

26

2.7

for INSTANZ1: schieberegister 4

28

use entity work.schieberegister 4(RTL2);

29

for RTL2

30

for GO

31

for G1

32

for BIT3: flipflop

33

use entity work.flipflop(D flipflop);

34

end for:

35

end for:

36

end for:

37

for others: flipflop

38

use entity work.flipflop(master_slave);

39

end for:

40

end for:

41

end for:

42

43

for INSTANZ2: schieberegister 4

44

use entity work.schieberegister_4(RTL2);

45

for RTL2

46

for all: flipflop

47

use entity work.flipflop(master_slave);

48

end for:

49

end for:

50

end for:

51

52.

end for:

53

end CFG1:

```

Der Nachteil dieses Ansatzes besteht darin, dass dem Designer einer hierarchisch aufgebauten Architektur die gesamte Hierarchie detailliert bekannt sein muss. Änderungen an Komponenten innerhalb der Hierarchie bedingen Änderungen in dem

Konfigurationsblock des obersten Bausteins. Bei größeren Entwürfen kann dies zu einem nicht unerheblichen Mehraufwand an Zeit führen.

■ Eine effizientere Art besteht darin, die in einer Architektur eines Bausteins vorkommenden Instanzen einer Komponente nicht an eine Architektur dieser Komponente zu binden, sondern an eine Konfiguration dieser Architektur. Hierzu stellt VHDL neben der use entity- die use configuration-Anweisung zur Verfügung.

```

configuration CFG2 of schieberegister 8 is

56

for RTI

57

for INSTANZ1: schieberegister_4

use configuration work.CFG2;

60

end for:

61

62

for INSTANZ2: schieberegister_4

63

use configuration work.CFG1a;

64

end for:

65

end for:

66

67

end CFG2:

```

Durch eine solche **use configuration**-Anweisung sind automatisch auch alle tiefer vorkommenden Komponenten-Instanzen an eine Realisierung gebunden.

Bei diesen Ausführungen wollen wir es belassen — wohl wissend, dass wir einige in VHDL enthaltene Aspekte wie zum Beispiel direkte Instanziierung von konfigurierten Komponenten und Belegung generischer Parameter während der Konfigurierung nicht angesprochen haben. Für eine Einführung in VHDL sollten aber die hier besprochenen Ansätze ausreichen. Für weitere, vertiefende Ausführungen verweisen wir auf das Buch von Ashenden [3].

#### 3.2 Variablen, Signale und Konstanten

Ein wichtiges Element zur Modellierung in VHDL sind Signale (und natürlich auch Variablen), die jeweils über einen Datentyp deklariert werden müssen. Signale modellieren Leitungen beziehungsweise Busse.

### 3.2.1 Deklaration von Variablen, Signalen und Konstanten

Die Deklaration von Variablen und Signalen ähnelt den Variablendeklarationen aus anderen Programmiersprachen. Insbesondere erlaubt VHDL auch eine Initialisierung der Variablen und Signale in der Deklaration, sodass eine Variablen- beziehungsweise Signaldeklaration das Aussehen

```

variable Variable_Name { , Variable_Name } :

Datentyp_Name [ := Ausdruck_vom_Datentyp_der_Variablen ] ;

signal Signal_Name { , Signal_Name } :

Datentyp_Name [ := Ausdruck_vom_Datentyp_der_Signale ] ;

```

hat. Mit einer ähnlichen Syntax kann man Konstanten deklarieren. In der Regel sieht eine solche Deklaration wie folgt aus:

```

constant Konstanten_Name :

Datentyp_Name :=Ausdruck_vom_Datentyp_der_Konstante ;

```

#### 3.2.2 Variablen- und Signalzuweisungen

Auf Variablen und Signale, insbesondere auf die Syntax einer Variablen- beziehungsweise Signalzuweisung, und auf ihre unterschiedliche Behandlung während der funktionalen Simulation sind wir in Abschnitt 2.2.1 detailliert eingegangen. Um diese Erläuterungen nicht nochmals an dieser Stelle wiederholen zu müssen, verweisen wir auf diesen Abschnitt und bauen im Folgenden auf die dort vermittelten Kenntnisse auf.

Damit können wir zur Vorstellung der Attribute, die auf Signalen definiert sind, zu sprechen kommen.

#### 3.2.3 Signalbasierte Attribute

Auf jedem Signal sind Attribute definiert, die dem Designer Informationen über das Signal geben. In der Regel generieren diese Attribute aus dem Signal ein neues, meist zeitversetztes Signal. Die zur Verfügung stehenden Attribute eines Signals s sind im Folgenden beschrieben. Dabei entspricht t stets einem Wert des physikalischen Datentyps time:

- Das Attribut s'delayed(t), welches ein Signal vom gleichen Datentyp wie Signal s darstellt, das die gleichen Werte wie das Signal s trägt, aber verzögert um t Zeiteinheiten.

- Das Attribut s'stable(t), das ein Signal vom Datentyp boolean ist und genau dann den Wert true trägt, wenn sich der Wert des Signals s in den letzten t Zeitschritten nicht geändert hat. Ist t gleich 0 ns, so ist s'stable(t) genau dann false, wenn sich in dem aktuellen Simulationsschritt der Wert des Signals s geändert hat.

- Das Attribut s'quiet(t), das ebenfalls ein Signal vom Datentyp boolean ist und genau dann gleich true ist, wenn während der letzten t Zeitschritte keine Zuweisung an das Signal s erfolgt ist beachten Sie bitte, dass eine Zuweisung an ein Signal nicht unbedingt eine Änderung der Signalbelegung zur Folge hat, sodass die Attribute s'stable(t) und s'quiet in der Regel verschieden sind.

- Das Attribut s'transaction, das ein Signal vom Datentyp bit ist. Es ändert seinen Wert in jedem Simulationszyklus, in welchem dem Signal s ein Wert zugewiesen wird.

- Das Attribut s'event, das ein Wert vom Datentyp boolean ist, der genau dann gleich true ist, wenn das Signal s in dem aktuellen Simulationszyklus seinen Wert ändert.

- Das Attribut s'active, das ein Wert vom Datentyp boolean ist, der genau dann gleich true ist, wenn dem Signal s in dem aktuellen Simulationszyklus ein Wert zugewiesen wird. Im Unterschied zum Attribut s'event braucht sich die Belegung des Signals s also nicht zu ändern.

- Das Attribut s'last\_event, das ein Wert vom Datentyp time ist, der die Zeit angibt, die vergangen ist, seitdem das Signal s das letzte Mal seinen Wert geändert hat. Ist bisher keine Wertänderung auf dem Signal erfolgt, so ist der Wert des Attributs gleich time'high (siehe Abschnitt 3.3.1).

- Das Attribut s'last\_active, das ein Wert vom Datentyp time ist, der die Zeit angibt, die vergangen ist, seitdem dem Signal s das letzte Mal ein Wert zugewiesen wurde. Ist bisher keine Wertzuweisung an das Signal erfolgt, so ist der Wert des Attributs gleich time' high (siehe Abschnitt 3.3.1).

- Das Attribut s'last\_value, das ein Wert vom gleichen Datentyp wie das Signal s ist. Es gibt den Wert zurück, das Signal s vor der letzten Wertänderung hatte. Ist bisher keine Wertänderung auf Signal erfolgt, so gibt das Attribut den Wert von s zurück.

- Die Attribute s'driving und s'driving\_value, auf deren nähere Erläuterung wir aber in diesem Buch verzichten wollen, da es weit über das hinaus ginge, was man in einem einführenden Buch zu VHDL erklären sollte und kann.

Wir kommen nun zu den Grundkonzepten, die VHDL neben den gerade vorgestellten Konstrukten package, entity, architecture und configuration sowie Signalen und Variablen bereitstellt.

#### 3.3 Datentypen und Subtypen

Lassen Sie uns mit den Datentypen beginnen.

#### Fallstrick 6

VHDL ist eine **streng getypte Programmiersprach**e. Dies besagt, dass einer Variablen beziehungsweise einem Signal nur Werte aus dem Datentyp (oder einem seiner Subtypen) zugewiesen werden dürfen, über den sie beziehungsweise es deklariert worden ist.

Betrachten Sie zum Beispiel die beiden Datentypen

```

type wortbreite is range 1 to 64;

type width is range 1 to 64;

```

Es handelt sich hierbei um zwei *verschiedene* Datentypen. Eine Zuweisung des Wertes einer Variablen vom Datentyp wortbreite an eine Variable des Datentyps width ist nicht erlaubt. Eine automatische Typentransformation erfolgt nicht.

Ähnliches gilt für die im Package standard (siehe Abschnitt 5.2) definierten Typen integer und real. Sie dürfen in arithmetischen Ausdrücken zum Beispiel nicht addiert werden, es sei denn einer von beiden wird explizit in den anderen Typtransformiert.

Eine explizite Typtransformation (oder -konvertierung), die naturgemäß nur zwischen "ähnlichen" Datentypen gemacht werden kann, erfolgt durch Voranstellen des Namens des Datentyps, in den konvertiert werden soll, gefolgt von dem, in Klammern eingerahmten, zu konvertierenden Wert:

```

Ziel_Datentyp (Wert)

```

Zum Beispiel konvertiert integer(3.2) den real-Wert 3.2 in den integer-Wert 3.

Welche Datentypen stellt VHDL nun zur Verfügung? In einem gewissen Sinne ist VHDL in dieser Beziehung recht nackt, da es an sich keinen spezifischen Datentyp für den Benutzer bereit hält. Vielmehr gibt uns VHDL Werkzeuge an die Hand, um uns die von uns benötigten Datentypen selbst zu definieren. Hierzu steht die **type-**Anweisung beziehungsweise die **subtype-**Anweisung zur Verfügung, die allgemein das Aussehen

|     | <b>type</b> Bezeichner <b>is</b> Datentyp_Spezifikation ; |  |

|-----|-----------------------------------------------------------|--|

| bez | iehungsweise                                              |  |

|     | subtype Bezeichner is Subtyp_Spezifikation;               |  |

haben.

Auf jedem Subtyp T (sogar auf jedem Datentyp T) ist das Attribut T'base definiert. T'base gibt den Basistyp an, über den der Datentyp T definiert ist.

Dieses Attribut darf nur im Zusammenhang mit anderen Attributen verwendet werden. Entsprechende Anwendungsbeispiele werden wir im Abschnitt über auf skalaren Datentypen definierte Attribute kennen lernen.

Prinzipiell unterscheidet VHDL zwischen den fünf Klassen

- Skalare Datentypen

- Felder

- Zeiger

- Verbunde

- Files

von Datentypen, wobei die skalaren Datentypen nochmals untergliedert sind in so genannte

- Integer-Datentypen

- Real-Datentypen

- Aufzählungstypen

- Physikalische Datentypen.

Wir wollen auf die Besonderheiten dieser Datentypen im Folgenden einzeln eingehen. Eigenschaften, die aus anderen Programmiersprachen wohl bekannt sind, werden wir nicht besprechen.

#### 3.3.1 Skalare Datentypen

Skalare Daten sind solche Daten, die sich nicht in andere Daten unterteilen lassen. In der Regel geht man davon aus — und dies ist auch der Fall in VHDL —, dass auf den Werten eines skalaren Datentyps eine totale Ordnung  $\leq$  definiert ist, sodass man die Werte entsprechend miteinander vergleichen kann.

VHDL erlaubt die wichtigsten Arten von skalaren Datentypen zu definieren: ganzzahlige und Gleitkommazahlen, Aufzählungstypen, sowie physikalische Datentypen. Letztere enthalten in ihren Wertebereichen ganzzahlige Zahlen, die mit einer (in der Regel physikalischen) Einheit versehen sind.

#### Integer-Datentypen

Integer-Datentypen sind Datentypen, die als Wertebereiche einen zusammenhängenden Bereich der ganzen Zahlen haben — in einem gewissen Sinne ist also jeder Integer-Datentyp ein Subtyp eines "anonymen" Datentyps, der als Wertebereich "alle" ganzen Zahlen enthält. Dieser anonyme Datentyp wird universal\_integer genannt. Der Basistyp eines jeden Integer-Datentyps ist somit der Datentyp universal\_integer.

Formal werden Integer-Datentypen über die Anweisungen

```

type Bezeichner is range Integer_Zahl to Integer_Zahl ;

type Bezeichner is range Integer_Zahl downto Integer_Zahl ;

```

definiert. Beispielsweise definiert

```

35    type monat_im_jahr is range 1 to 12;

```

einen Integer-Datentyp, der aus 12 ganzzahligen Werten besteht, nämlich aus den ganzen Zahlen 1 bis 12.

Auf Integer-Datentypen sind neben den Vergleichsoperatoren = (gleich), /= (verschieden), < (echt kleiner), <= (kleiner gleich), > (echt größer) und >= (größer gleich) die für ganze Zahlen üblichen Operationen

- Addition +.

- Subtraktion –,

- Multiplikation \*,

- ganzzahlige Division /,

- Potenzierung \*\*,

- Absolutwert **abs**,

- Modulo-Berechnung mod

- Rest bei der ganzzahligen Division **rem**

definiert.

#### **Exkurs: Modulo-Berechnung und Rest-Bildung**

Die Modulo-Berechnung  $x \mod y$  und die Bestimmung des Restes  $x \operatorname{rem} y$  bei der ganzzahligen Division von x durch y sind im Falle von  $y \in \mathbb{N}$  sehr ähnliche Operationen.

- In der Tat, ist *x* eine nichtnegative ganze Zahl, so unterscheiden sich beide Operationen nicht.

- Unterschiedliche Ergebnisse erhält man jedoch in der Regel, wenn x eine negative ganze Zahl ist. Während die Division gegen die Null rundet, also zum Beispiel -19 div 8=-2 und somit -19 rem 8=-3 gilt, bildet die Modulo-Berechnung den Wert x in eine der Restklassen  $0, \ldots, y-1$  ab. In unserem Beispiel gilt somit -19 mod 8=5.

Beide Operationen, wie auch die Division selbst, können in der Regel nur dann durch Synthese-Werkzeuge synthetisiert werden, wenn der Divisor y eine Zweierpotenz ist, da in diesem Fall die Operationen im Wesentlichen durch einen Shift, also recht einfach, realisiert werden können.

Integer-Konstanten lassen sich neben der uns gebräuchlichen Schreibweise zur Basis 10 auch zu anderen Basen aus dem Bereich zwischen 2 und 16 in VHDL schreiben. Das allgemeine Format ist durch

Basis#Darstellung\_zu\_der\_angegebenen\_Basis#

gegeben. So kann der Integer-Wert 123 nicht nur durch

123,

sondern auch durch

2#1111011#.

durch

8#173#,

durch

16#7B#

und so weiter dargestellt werden.

Zusätzlich kann eine (lange) Integer-Konstante zur besseren Lesbarkeit zwischen je zwei Ziffern einen Unterstrich enthalten. In diesem Sinne sind die Schreibweisen

```

-2#111001010#,

-2#1 1100 1010#

```

und

-16#1CA#

alle drei erlaubt und beschreiben den gleichen Integer-Wert, nämlich den Wert -458. Negative Werte werden durch ein vorangestelltes Minus vor der Basis kenntlich gemacht.

VHDL stellt über die Bibliothek standard (siehe Abschnitt 5.2), die stets implizit bei einem Entwurf eingebunden ist,

- den Integer-Datentyp integer, sowie

- die beiden Subtypen natural und positive des Datentyps integer zur Verfügung, welche die nichtnegativen beziehungsweise die positiven Werte des Datentyps integer umfassen.

Der Bereich von  $-2^{31}+1$  bis  $2^{31}-1$  ist als Mindestanforderung für den Wertebereich des Datentyps integer an VHDL-Implementierungen vorgegeben. VHDL-Implementierungen dürfen und stellen auch zum Teil größere Bereiche — meist wird der von der 32-Bit Zweierkomplement-Zahlendarstellung verwendete Bereich  $-2^{31}$  bis  $2^{31}-1$  bereitgestellt — für den Integer-Datentyp integer zur Verfügung gestellt. In diesem Zusammenhang sind die auf jedem skalaren Datentyp definierten Attribute low and high sehr nützlich. Sie geben den kleinsten beziehungsweise den größten Wert eines skalaren Datentyps zurück. So liefert uns integer'low den kleinsten Wert, integer'high den größten Wert des Integer-Datentyps integer.

Mehr zu Attributen im Allgemeinen finden Sie im Abschnitt 3.6 auf Seite 114. Eine Liste der auf skalaren Datentypen definierten Attribute finden Sie auf Seite 86.

#### **Real-Datentypen**

Analog zu den gerade vorgestellten Integer-Datentypen gibt es die so genannten Real-Datentypen, die jeweils einen zusammenhängenden Bereich von Gleitkommazahlen darstellen. Die Typdefinition eines Real-Datentyps hat im Wesentlichen das gleiche Aussehen wie das, was wir bei den Integer-Datentypen schon kennen gelernt haben:

type Bezeichner is range Gleitkommazahl to Gleitkommazahl ;

type Bezeichner is range Gleitkommazahl downto Gleitkommazahl ;

Auf ihnen sind ebenfalls die üblichen Vergleichsoperatoren und arithmetischen Operatoren definiert.

Real-Konstanten lassen sich unter Verwendung unterschiedlicher Basen aus dem Bereich 2 bis 16 in Gleitkommadarstellung schreiben. So stellen die Darstellungen 0.75, 75.0e-2 und 7.5E1 (zur Basis 10) jeweils die gleiche Zahl 0.75 dar. Wählt man eine andere Basis, so wird eine ähnliche Schreibweise wie bei den Integer-Datentypen verwendet, wobei ein möglicher Exponent hinter das zweite #-Zeichen als Dezimalzahl geschrieben wird und als Exponent zur angegebenen Basis zu verstehen ist. So beschreibt die Darstellung 2#11.0#e-3 den Wert  $3 \cdot 2^{-3}$ , also den Wert 0.375.

Die implizit eingebundene Bibliothek standard (siehe Abschnitt 5.2) stellt den Real-Datentyp real zur Verfügung, der als Wertebereich mindestens den Bereich von  $-1.7014110 \cdot 10^{38}$  bis  $1.7014110 \cdot 10^{38}$  umfasst. Die genauen Grenzen können, wie beim Datentyp integer oder anderen Integer-Datentypen, über die Attribute real 'low und real'high festgestellt werden.

Der Wertebereich des Datentyps real kann wie der Datentyp integer von der benutzten VHDL-Implementierung abhängen.

#### Physikalische Datentypen

Eine Besonderheit von VHDL im Vergleich zu anderen Programmiersprachen ist die Möglichkeit, physikalische Datentypen definieren zu können. Sie werden angewendet, um einfach mit physikalischen Größen, wie zum Beispiel Längen-, Gewichts-, Geschwindigkeits- und Zeitangaben und Ähnlichem arbeiten zu können. So ist jedem physikalischen Datentyp neben einem Bereich von Integer-Werten eine *primäre Einheit* zugeordnet, in der die Angaben gemessen werden. Zu der primären Einheit kann es weitere Einheiten, so genannte *sekundäre Einheiten*, geben, die ein Vielfaches der primären Einheit darstellen müssen.

Lassen Sie uns auf eine formale Definition der Syntax physikalischer Datentypen verzichten und uns einfach nur zwei, drei Beispiele anschauen.

Der Quellcode

```

type laenge_einfach is range 0 to 1E9

units km;

end units laenge_einfach;

```

definiert einen physikalischen Datentyp mit Namen laenge\_einfach, für den keine sekundären Einheiten definiert sind, sondern nur eine primäre Einheit — die primäre Einheit km, die für Kilometer stehen soll. Der Zahlenbereich erstreckt sich von dem Integer-Wert 0 bis zum Integer-Wert 10<sup>9</sup>. Dieser physikalische Datentyp ist an sich nichts anderes als ein Integer-Datentyp, der mit einer Einheit versehen ist; er würde den Vorteil, den physikalische Datentypen bieten, nämlich die "automatische Umrechnung" zwischen den definierten Einheiten, nicht nutzen und würde demnach auch keinen großen Sinn ergeben. Die eigentlichen Vorteile physikalischer Datentypen würde hingegen der physikalische Datentyp laenge

```

39

type laenge is range -2147483647 to 2147483647

40

units nm:

41

um = 1000 nm;

-- Mikrometer

42

mm = 1000 \text{ um}:

-- Millimeter

43

10 mm;

-- Centimeter

44

100 cm;

-- Meter

45

Zoll = 25400 \text{ um}:

-- Zoll oder Inch

46

end units laenge:

```

bieten.

Auf den physikalischen Datentypen sind die üblichen Vergleichsoperatoren sowie Addition, Subtraktion, Absolutwert und Division von physikalischen Werten definiert.

#### Fallstrick 7

Die Division zweier Werte eines physikalischen Datentyps ergibt einen Integer-Wert. Somit ist der Ausdruck

```

10 \text{ Zoll} + (3 \text{ m} / 10 \text{ mm})

```

nicht zulässig, da ein Wert vom Datentyp laenge mit einem Integer-Wert addiert werden würde. Dies ist in VHDL, die eine streng getypte Programmiersprache ist, nicht erlaubt.

Einen Integer-Wert kann man in einen physikalischen Wert, sagen wir in einen Wert vom physikalischen Datentyp laenge, umwandeln, d. h. konvertieren, indem man den Integer-Wert mit einem der physikalischen Werte multipliziert. In unserem Beispiel bietet sich hierfür der Wert 1 nm an.

Physikalische Werte können demnach mit ganzen Zahlen multipliziert beziehungsweise dividiert werden.

In den "arithmetischen" Ausdrücken können wir verschiedene Einheiten benutzen. So ist zum Beispiel der Ausdruck

$$10 \text{ Zoll} + (3 \text{ m} / 2)$$

erlaubt. Der VHDL-Simulator rechnet alle physikalischen Operatoren eines solchen Ausdrucks auf die primäre Einheit des entsprechenden physikalischen Datentyps zurück — in unserem Beispiel auf nm.

Physikalische Werte miteinander zu multiplizieren, ist in VHDL *nicht* erlaubt. In der Tat, es macht auch keinen großen Sinn. Die Multiplikation von zwei Längeneinheiten ergibt eine Flächeneinheit und ist somit kein Wert aus dem Wertebereich des gegebenen physikalischen Datentyps. Will man dennoch physikalische Werte — was auch immer der Grund hierfür sein möge — miteinander multiplizieren, kann man dies über die, auf skalaren Datentypen definierten, Attribute pos und val realisieren. Lassen Sie uns diese beiden Attribute — eine vollständige Aufzählung der auf physikalischen Datentypen definierte Datentypen folgt in Abschnitt 3.3.1 — beispielhaft an unserem Datentyp laenge erklären

- Das Attribut laenge'pos(X) angewendet auf einen Wert X des physikalischen Datentyps laenge gibt den dazu gehörigen Integer-Wert in Bezug auf die primäre Einheit zurück. Beispiel: laenge'pos(3 cm) ist gleich 30 000 000.

- Das Attribut kann somit als Datentypkonvertierungeines physikalischen Wertes in einen Integer-Wert benutzt werden.

- Das Attribut laenge'val(X) wird auf einen Integer-Wert X angewendet und gibt dann den entsprechenden Wert des physikalischen Datentyps laenge zurück, ist also in einem gewissen Sinne die inverse Funktion zu dem Attribut laenge'pos().

VHDL stellt standardmäßig über die Library standard den physikalischen Datentyp time bereit. Näheres zu diesem speziellen Datentyp ist in Abschnitt 5.2.2 auf Seite 136 zu finden.

#### Aufzählungstypen

Die Aufzählungstypen sind die einfachsten skalaren Datentypen. Hier werden die in dem Wertebereich verfügbaren Werte in der Datentypdefinition einfach nur aufgezählt. Die Reihenfolge, in der das passiert, bestimmt die auf dem Datentyp definierte totale Ordnung ≤. Allgemein hat die Definition eines Aufzählungstyp das Aussehen

```

type Bezeichner is ( Element { , Element } );

```

Beispiele von solchen Aufzählungstypen sind in den in Kapitel 5 vorgestellten Packages zu finden. Im Package standard (siehe Abschnitt 5.2 Seite 133) zum Beispiel, das implizit in VHDL eingebunden ist, werden die Aufzählungstypen

- boolean, der aus den Werten false und true mit false<true besteht,

- bit, der aus den Werten '0' und '1' mit '0' ≤ '1' besteht,

- character, der die 128 Zeichen des Maschinenalphabets umfasst,

- severity\_level, der aus den Werten note, warning, error und failure besteht; ein Datentyp, der im Rahmen der **assert**-Anweisung (siehe Abschnitt 3.4 und Abschnitt 3.5 auf den Seiten 110–112) von Bedeutung ist, sowie

- die Aufzählungstypen file\_open\_kind und file\_open\_status, die im Rahmen des Zugriffs auf Dateien benötigt werden (siehe Abschnitt 5.2.4),

definiert.

Das Package stg\_logic\_1164 (siehe Abschnitt 5.3) stellt eine 9-Werte-Logik zur Verfügung, die über einen Aufzählungstyp namens std\_ulogic (beziehungsweise std\_logic) definiert ist und die es ermöglicht, Hardware realitätsnäher zu beschreiben und zu simulieren als dies mit dem Datentyp bit zum Beispiel möglich ist.

Anwendung finden Aufzählungstypen oft bei der Beschreibung von endlichen Automaten zur Festlegung der möglichen Zustände:

```

8 type state is (idle, start, stopp);

```

#### Auf skalaren Datentypen definierte Attribute

Auf jedem skalaren Datentyp T sind, neben dem, schon auf jedem Datentyp definierten Attribut T'base, das den Basistyp des Datentyps T angibt, weitere Attribute definiert, die dem Designer Informationen zu dem Datentyp geben. Unabhängig von der Art des skalaren Datentyps stehen die sieben Attribute

- T'high, welches den größten Wert des Datentyps T liefert,

- T'low, welches den kleinsten Wert des Datentyps T liefert,

- T'left, das den Wert der linken Bereichsgrenze des Datentyps T angibt,

- T'right, das den Wert der rechten Bereichsgrenze des Datentyps T angibt,

- T'ascending, das vom Datentyp boolean ist und genau dann gleich dem Wert true ist, wenn der zu T gehörige Wertebereich aufsteigend ist, also über eine **to**-Anweisung (und nicht über eine **downto**-Anweisung) definiert wurde,

- T'image(X), das eine Funktion darstellt, die angewendet auf einen Wert X aus dem Wertebereich von T einen Wert vom Datentyp string (siehe Abschnitt 5.2), der eine textuelle Darstellung des Wertes X ist, zurückgibt.

- T'value(X), das, informal ausgedrückt, die zu der Funktion T'image() inverse Funktion darstellt. Angewendet auf eine Zeichenfolge X versucht diese Funktion diese Zeichenfolge als Wert des Datentyps T zu interpretieren und gibt diesen Wert zurück.

zur Verfügung.

Ist T ein Aufzählungstyp, so gilt T'low=T'left und T'high=T'right. Bei einem Integer-Datentyp T gelten diese beiden Gleichungen nur dann, wenn das Attribut T'ascending wahr ist.

Nur auf Aufzählungstypen, Integer-Datentypen und physikalischen Datentypen sind die folgenden Attribute definiert:

■ Das Attribut T'pos(X), das eine Funktion darstellt, die, angewendet auf einen Wert X aus dem Wertebereich des Datentyps T, die Position des Wertes X im Datentyp T zurückgibt. Der zurückgegebene Wert ist von dem speziellen Datentyp universal\_integer.

Der Begriff "Position" ist in Abhängigkeit der Art des skalaren Datentyps unterschiedlich definiert:

- Die Position eines Wertes X eines Aufzählungstyps ist als die Stelle definiert, an der der Wert X in der totalen Ordnung des Aufzählungstyps steht. Der erste in der totalen Ordnung vorkommende Wert hat Position 0.

- Die Position eines Wertes X eines Integer-Datentyps ist der Wert X selbst—jedoch als Wert des Datentyps universal\_integer interpretiert.

- Die Position eines Wertes X eines physikalischen Datentyps ist der Integer-Wert des Wertes X, ausgedrückt über die primäre Einheit dieses physikalischen Datentyps.

- Das Attribut T'val(X), das eine Funktion darstellt, die, angewendet auf einen Integer-Wert X, den X-ten Wert aus dem Wertebereich des Datentyps T zurückgibt.

- Das Attribut T'succ(X), das eine Funktion darstellt, die, angewendet auf einen Wert X aus dem Wertebereich des Datentyps T, den Wert aus dem Wertebereich des Basistyps von T zurückgibt, der in der totalen Ordnung des Basistyps von T dem Wert X direkt folgt. Es gilt also

T'base'pos(T'succ(X)) = T'base'pos(X)+1.

Ist X schon das größte Element T'base'high aus dem Basistyp von T, so ist der Funktionswert T'succ(X) nicht definiert.

■ Das Attribut T'pred(X), das eine Funktion darstellt, die, angewendet auf einen Wert X aus dem Wertebereich des Datentyps T, den Wert aus dem Wertebereich des Basistyps von T zurückgibt, der in der totalen Ordnung des Basistyps von T genau vor dem Wert X steht. Es gilt also

```

T'base'pos(T'pred(X)) = T'base'pos(X)-1.

```

Ist X schon das kleinste Element T'base'low aus dem Basistyp von T, so ist der Funktionswert T'pred(X) nicht definiert.

- Das Attribut T'leftof(X), das eine Funktion darstellt, die, angewendet auf einen Wert X aus dem Wertebereich des Datentyps T, den links von ihm stehenden Wert im Wertebereich des Basistyps von T zurückgibt.

- Ist X schon das am weitesten links stehende Element T'base'left aus dem Basistyp von T, so ist der Funktionswert T'leftof(X) nicht definiert.

- Das Attribut T'rightof(X), das eine Funktion darstellt, die, angewendet auf einen Wert X aus dem Wertebereich des Datentyps T, den rechts von ihm stehenden Wert im Wertebereich des Basistyps von T zurückgibt.

- Ist X schon das am weitesten rechts stehende Element T'base'right aus dem Basistyp von T, so ist der Funktionswert T'rightof(X) nicht definiert.

#### 3.3.2 Zusammengesetzte Datentypen

Lassen Sie uns damit zu den so genannten zusammengesetzten Datentypen kommen. Die von VHDL bereitgestellten Möglichkeiten, Zeiger zu deklarieren, wollen wir in diesem Abschnitt ebenfalls behandeln — auch wenn es sich hierbei nicht um einen zusammengesetzten Datentyp handelt —, da sie (fast inhärent) eng mit Verbunden (engl.: records) zusammenhängen.

#### Felder

Felder (engl.: *arrays*) setzen sich in VHDL, wie in jeder anderen Programmiersprache auch, aus Elementen des gleichen Datentyps zusammen. Es gibt in VHDL sowohl eindimensionale Felder, d. h. Felder, bei denen die Komponenten über nur einen Index indiziert sind, als auch mehrdimensionale Felder mit mehreren Indizes. Hierbei unterscheidet VHDL zwischen so genannten beschränkten (engl.: *constrained*) Feldern und unbeschränkten (engl.: *unconstrained*) Feldern.

#### Beschränkte Felder

Beschränkte Felder sind dadurch gekennzeichnet, dass der Wertebereich der Indizes durch Angabe einer unteren und oberen Grenze fest vorgegeben ist. Eine entsprechende Typdefinition sieht bei eindimensionalen Feldern (in der Regel) wie folgt aus:

```

type Bezeichner is array

( Diskreter_Werte_Bereich ) of Datentyp_Name ;

```

Bei mehrdimensionalen beschränkten Feldern werden die Wertebereiche einfach nur durch jeweils ein Komma getrennt.

```

type Bezeichner is array

( Diskreter_Wertebereich { , Diskreter_Wertebereich } )

of Datentyp_Name ;

```

Als Beispiel seien hier angeführt

```

47    type byte is array (7 downto 0) of bit;

48    type wort is array (1 to 4) of byte;

49    type ram is array (0 to 1023) of wort;

50    type brett is array (positive range 1 to 9,

51    positive range 1 to 9) of integer;

```

oder der in der Implementierung des Packages std\_logic\_1164 benutzte Feld-Datentyp

```

type stdlogic_table is array(std_ulogic, std_ulogic)

f std_ulogic;

```

der als Wertebereich der beiden Indizes den Aufzählungstyp std ulogic hat.

Komponentenweise Zugriffe oder Belegungen erfolgen durch Angabe des Bezeichners (Name der Variablen, des Signals oder der Konstante), gefolgt von den, in runden Klammern eingeschlossenen Indexwerten. Der Zugriff auf die Komponente 173 der Variable ram\_var erfolgt also durch ram\_var(173). Für den feldweisen Zugriff oder die feldweise Belegung stehen mehrere Methoden zur Verfügung. Im Codefragment

```

98 byte_a <= ('0','0','0','1','1','1','1','0');

99 byte_b <= (4 | 3 | 2 | 1 => '1', others => '0');

100 byte_c <= (4 downto 1 => '1', others => '0');

```

in dem byte\_a, byte\_b, byte\_c Signale vom Datentyp byte darstellen, sind einige mögliche Kombinationen gezeigt.

Die Belegung von mehrdimensionalen Feldern ist ähnlich einfach. Wie das Beispiel in Abbildung 3.7, in dem eine Konstante namens kleines\_Einmaleins von dem oben definierten Datentyp brett definiert wird, zeigt, können zweidimensionale Felder — der erste Index eines zweidimensionalen Feldes steht für die Zeilen, der zweite Index für die Spalten — "zeilenweise" belegt werden, d. h. man gibt zuerst den zur ersten Zeile

```

57

-- Funktionstafel des kleinen Einmaleins

58

constant kleines_Einmaleins : brett := (

59

60

1

3

5

6

7

61

62.

2,

3.

4.

5.

6. 7.

8.

9).

63

2.

6.

8, 10, 12, 14, 16, 18).

4.

9. 12. 15. 18. 21. 24. 27 ).

64

3. 6.

65

4, 8, 12, 16, 20, 24, 28, 32, 36),

( 5, 10, 15, 20, 25, 30, 35, 40, 45),

( 6, 12, 18, 24, 30, 36, 42, 48, 54 ),

67

( 7, 14, 21, 28, 35, 42, 49, 56, 63 ),

68

( 8, 16, 24, 32, 40, 48, 56, 64, 72 ),

69

( 9, 18, 27, 36, 45, 54, 63, 72, 81)

70

71

):

```

Abbildung 3.7: Deklaration und Definition eines zweidimensionalen Feldes als Konstante

gehörigen eindimensionalen Vektor an, dann den zur zweiten Zeile gehörigen und so weiter. In unserem Beispiel gilt für alle Werte i und j aus dem Wertebereich 1 bis 9

```

kleines_Einmaleins(i,j) = i*j.

```

VHDL stellt verschiedene Möglichkeiten zur Verfügung, um so genannte *Bitfolgen* bequem schreiben zu können. Ursprünglich nur für Felder über dem Datentyp bit gedacht, sind diese Schreibweisen seit VHDL'93 für alle eindimensionalen Arrays erlaubt, die über einem Aufzählungstyp definiert sind und die Zeichen '0' und '1' enthalten.

Bitfolgen kann man in binärer, in oktaler oder in hexadezimaler Darstellung schreiben. Die Darstellungsart wird durch den Präfix, der entweder B, 0 oder X ist, angegeben. Die Darstellung selbst folgt dann als endliche Folge über  $\{0,1\}$ , über  $\{0,1,\ldots,7\}$  beziehungsweise über  $\{0,1,\ldots,9,A,B,C,D,E,F\}$  umrahmt mit dem "-Zeichen.

```

So stellen zum Beispiel

```

```

0"4731" die Bitfolge "100111011001"

```

und

X"9DA" die Bitfolge "100111011010" dar.

Zu beachten ist, dass eine oktal dargestellte Bitfolge immer ein (eindimensionales) Feld darstellt, dessen Länge ein Vielfaches von 3 ist; eine hexadezimal dargestellte Bitfolge immer ein Feld, dessen Länge ein Vielfaches von 4 ist.

#### Unbeschränkte Felder

Bei unbeschränkten Feldern legt man sich bei der Definition des Datentyps nicht auf genaue Grenzen für den Index beziehungsweise die Indizes fest, sondern verschiebt die

Festlegung auf später, zum Beispiel auf den Zeitpunkt der Variablendeklaration. So werden in dem Package standard (siehe Abschnitt 5.2) die Datentypen

```

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

und in dem Package std_logic_1164 (siehe Abschnitt 5.3) die Datentypen

type std_ulogic_vector is array ( natural range <> )

```

zur Verfügung gestellt. Sie definieren jeweils unbeschränkte Felder. Die Grenzen der

Indexbereiche sind nicht durch die Definition des Datentyps festgelegt. Die formale Syntax, um unbeschränkte Felder zu definieren, ist durch

```

type Bezeichner is array

( Diskreter_Datentyp range <> { , Diskreter_Datentyp <> } )

of Datentyp_Name ;

```

gegeben.

38

Unbeschränkte Felder finden ihre Anwendung

of std logic:

- in Packages, wo sie es ermöglichen, von der Größe der Wertebereiche unabhängige Felder vorzudefinieren. Mit den im Package std\_logic\_1164 definierten Datentypen std\_ulogic\_vector und std\_logic\_vector haben wir gerade zwei solche Beispiele erwähnt.

- Als formale Parameter von Funktionen und Prozeduren (siehe Kapitel 4). Hier werden die exakten Wertebereiche erst durch die aktuellen Parameter festgelegt.

- Als Ports von Bausteinen, wobei sie naturgemäß dann nicht nur im Rahmen der entity-Definition, sondern auch in den dazugehörigen Architekturen benutzt werden. Erst bei der Instanziierung einer Komponente dieses Bausteins werden den unbeschränkten Ports beschränkte Felder zugewiesen. Ein ausführliches Beispiel einer solchen Schnittstellenbeschreibung (mit zugehöriger Architektur) ist in Abschnitt 3.5 auf Seite 113 zu finden.

Wir wollen die Effektivität unbeschränkter Felder an einer Prozedur illustrieren, die eine n-Bit Zweierkomplement-Zahlendarstellung in eine m-Bit-Zweierkomplement-Darstellung mit  $m \ge n$  umwandelt. Wie in den Exkursen zu Zweierkomplement-Darstellung und

Vorzeichenverdopplung in Kapitel 6 noch ausführlich erläutert wird, ist zur Realisierung einer solchen Erweiterung das Vorzeichen der n-Bit-Zweierkomplement-Darstellung m-n Mal zu kopieren und der n-Bit-Zweierkomplement-Darstellung voranzustellen. Abbildung 3.8 zeigt eine der möglichen Realisierungen.

```

19

procedure sign extend (

20

inp: in std logic vector:

2.1

result: out std_logic_vector ) is

22

23

assert inp'length <= result'length</pre>

24

report "Der Ausgabevektor ist zu kurz!"

25

severity failure;

assert (inp'right = 0) and (result'right = 0)

2.6

27

report "Attribut 'right muss jeweils Index 0 liefern!"

28

severity failure:

29

result(inp'length-1 downto 0) := inp;

for i in inp'length to result'length-1 loop

30

31

result(i) := inp(inp'length-1);

32

end loop:

33

end:

```

Abbildung 3.8: Prozedur zur Transformation einer Zweierkomplement-Darstellung auf einer größere Wortbreite

Wie man sieht, wird in der Definition der Prozedur sign\_extend weder die Länge des formalen Eingabeparameters inp - über das Schlüsselwort in wird festgelegt, dass es sich bei diesem Parameter um einen Eingabeparameter handelt - noch die Länge des formalen Ausgabeparameters result festgelegt. Erst bei Aufruf der Prozedur wird über die aktuellen Parameter die Länge dieser beiden Felder bestimmt. Um etwaige Fehler, die letztendlich auf die durch die Nicht-Festlegung der Bereichsgrenzen der formalen Parameter bedingten Freiheiten zurückzuführen sind, während der Laufzeit zu finden in unserem Beispiel sollte der Ausgabeparameter nicht kürzer als der Eingabeparameter sein; zudem sollten die Felder von rechts her mit 0 beginnend aufwärts indiziert sein sollte eine solche Prozedur überprüfen, ob die aktuellen Parameter den Voraussetzungen genügen. Dies erfolgt in der Regel über die auf Feldern definierten Attribute. In unserer Beispielprozedur erhalten wir die Längen der beiden Felder über die Attribute inp'length und result'length. Ist der erste Wert echt größer als der zweite Wert, so wird über die assert-Anweisung eine Fehlermeldung ausgegeben. Über die Attribute inp'right und result'right überprüfen wir, ob die rechten Komponenten der beiden Feldern den Index 0 haben.

#### Attribute auf Feldern

Lassen Sie uns detaillierter auf die auf Feldern definierten Attribute zu sprechen kommen. Sei hierzu A ein über einem Datentyp  $\top$  definiertes k-dimensionale Feld und  $\mathbb N$  ein beliebiger Integer-Wert aus dem Bereich von 1 bis k. Folgende auf Feldern definierte Attribute stellt uns VHDL zur Verfügung:

- Das Attribut A'length(N), das uns die Größe des N-ten Indexbereiches von A angibt.

- Das Attribut A'left(N), das den linken Rand des N-ten Indexbereiches von A angibt; das Attribut ist also von dem gleichen Datentyp wie die Indizes der N-ten Dimension des Feldes A.

- Das Attribut A'right(N), das den rechten Rand des N-ten Indexbereiches von A angibt; das Attribut ist also ebenfalls von dem gleichen Datentyp wie die Indizes der N-ten Dimension des Feldes A.

- Das Attribut A'low(N), das den kleinsten Wert des N-ten Indexbereiches von A angibt; dieser Wert ist je nachdem, ob in der Definition des Datentyps von A downto oder to zur Spezifikation des Indexbereiches benutzt wurde, gleich dem Wert A'left.

- Das Attribut A'high(N), das den größten Wert des N-ten Indexbereiches von A angibt. Dies ist je nachdem, ob in der Definition des Datentyps von A **downto** oder **to** zur Spezifikation des Indexbereiches benutzt wurde, gleich dem Wert A'left oder dem Wert A'right.

- Das Attribut A'range(N), das den Wertebereich des N-ten Indexbereiches von A angibt. Dies erlaubt uns auch bei unbeschränkten Feldern alle Komponenten zu durchlaufen. Wir werden, nachdem wir uns das nächste Attribut angesehen haben, ein kleines Beispiel dazu angeben.

- Das Attribut A'reverse\_range(N), das den gespiegelten Wertebereich des N-ten Indexbereiches von A angibt. Ist A zum Beispiel ein zweidimensionales Feld, so durchforstet der Programmcode

```

for i in A'range(1) loop

for j in A'reverse_range(2) loop

report positive'image(A(i,j));

end loop;

end loop;

```

Das Feld A, wobei der Indexbereich der ersten Dimension in der Reihenfolge beginnend mit A'left(1) hin zu A'right(1) und der Indexbereich der zweiten Dimension in umgekehrter Reihenfolge, also von A'right(2) hin zu A'left(2) durchlaufen wird.

■ Das Attribut A'ascending(N), das vom Typ boolean ist und genau dann gleich true ist, wenn der N-te Indexbereich monoton steigend ausgelegt ist, d. h. über das Schlüsselwort **to** (und nicht über das Schlüsselwort **downto**) definiert wurde.

Der Parameter N ist optional. Defaultmäßig ist er mit dem Wert 1 vorbelegt.

Einige der Attribute sind sehr nahe miteinander verwandt. So gilt beispielsweise

```

A'ascending(N) = true \implies A'left(N) = A'low(N)

A'ascending(N) = true \implies A'right(N) = A'high(N)

```

```

A'ascending(N) = false \implies A'left(N) = A'high(N)

A'ascending(N) = false \implies A'right(N) = A'low(N).

```

Ist der N-te Indexbereich über Integer-Werte definiert, so gilt desweiteren

```

A'length = A'high(N) - A'low(N) + 1.

```

#### **Operationen auf Feldern**

Die in VHDL zur Verfügung gestellten Operationen auf Feldern beziehen sich alle nur auf eindimensionale Felder, die meisten sogar nur auf eindimensionale Felder, die über dem Datentyp bot dem Datentyp boolean definiert sind. Es sind dies

- Die binären logischen Operationen and, or, nand, nor, xor, und xnor, die nur auf eindimensionalen Feldern über dem Datentyp boolean oder bit gleicher Länge definiert sind. Ergebnis der Operationen ist jeweils die komponentenweise ausgeführte logische Basisoperation.

- Die Shift- und Rotate-Operatoren

- Der Operator s11, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach links schiebt (engl.: shift-left logical). Rechts werden die Stellen mit dem Wert '0' beziehungsweise false aufgefüllt. So gilt zum Beispiel

```

B"10110011" s11 2 = B"11001100".

```

Der Operator sr1, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach rechts schiebt (engl.: shift-right logical). Links werden die Stellen mit dem Wert '0' beziehungsweise false aufgefüllt. So gilt zum Beispiel

```

B"10110011" srl 2 = B"00101100".

```

Der Operator sla, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach links schiebt (engl.: shift-left arithmetic). Rechts werden die Stellen mit dem Wert aufgefüllt, der ursprünglich an der hinteren Stelle des Vektors stand. So gilt zum Beispiel

```

B"10110011" sla 2 = B"11001111".

```

Der Operator sra, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach rechts schiebt (engl.: shift-right arithmetic). Links werden die Stellen mit dem Wert aufgefüllt, der ursprünglich an der vorderen Stelle des Vektors stand. So gilt zum Beispiel

```

B"10110011" sra 2 = B"11101100".

```

Der Operator rol, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach links rotiert (engl.: rotate-left). Die links "herunter fallenden" Werte werden rechts wieder angehängt. So gilt zum Beispiel

```

B"10110011" rol 2 = B"11001110".

```

Der Operator ror, der, angewendet auf einen Vektor vom Datentyp bit oder boolean, diesen um eine bestimmte Anzahl von Stellen nach rechts rotiert (engl.: rotate-right). So gilt zum Beispiel

```

B"10110011" \text{ ror } 2 = B"11101100".

```

Während der linke Operand bei den Shift- und Rotate-Operationen der zu verändernde Vektor ist, gibt der rechte Operand die Anzahl der Stellen an, um die geschoben beziehungsweise rotiert werden soll. VHDL erlaubt, dass dieser rechte Operand auch eine negative ganze Zahl sein darf. In diesem Fall wird ein Richtungswechsel vollzogen, d.h. ein Links-Shift wird zu einem Rechts-Shift, Links-Rotation wird zu Rechts-Rotation und umgekehrt.

- Die Vergleichsoperatoren =, /=, <, <=, > und , die zwei über den gleichen Datentyp definierte eindimensionale Felder lexikografisch miteinander vergleichen.

- Die Konkatenation & zweier Felder, die eindimensionale, über dem gleichen Datentyp definierte Felder zu einem Feld verschmelzt. So beschreibt der Quellcode

```

9

procedure unsigned2signed (

10

inp: in std_logic_vector;

11

result: out std logic vector ) is

12

begin

13

assert inp'length = result'length-1

14

report "Die Vektoren haben falsche Längen"

15

severity failure;

16

result := '0' & inp;

17

end:

```

eine Prozedur, die eine Binärzahl (ohne Vorzeichen) in eine vorzeichen-behaftete Darstellung überführt.

Damit wollen wir mit den **array**-Datentypen schließen und uns Verbunde und Zeiger anschauen.

#### Verbunde

Neben (beschränkten und unbeschränkten) Feldern stellt VHDL, wie die meisten anderen Programmiersprachen auch, noch eine zweite Klasse von zusammengesetzten Datentypen zur Verfügung: die *Verbunde* (engl.: *records*). Im Unterschied zu Feldern, deren Komponenten alle vom gleichen Typ sind, fasst ein Verbund Werte unterschiedlicher Datentypen in einem Objekt zusammen. So definieren wir beziehungsweise deklarieren wir mit

```

9

type ethernet frame format is

10

praeambel: std_logic_vector(0 to 63);

11

zieladresse: std logic vector(47 downto 0);

12

quelladresse: std_logic_vector(47 downto 0);

13

14

schluessel: std_logic_vector(0 to 15);

15

nachricht: std logic vector(1 to 368);

crc: std logic vector(31 downto 0):

16

17

end record:

18

signal ethernet_paket: ethernet_frame_format;

```

einen Datentyp, dessen Werte Ethernet-Pakete darstellen, und ein Signal namens ethernet\_paket von diesem Datentyp. Ein Ethernet Paket besteht aus sechs Komponenten, die als Felder unterschiedlicher Länge über dem Datentyp std\_logic deklariert sind<sup>6</sup>. Es sind dies die Komponenten

- praeambel, die 64 Bit lang ist und alternierend aus '0' und '1' besteht; sie erlaubt dem Empfänger, sich mit dem ankommenden Signal zu synchronisieren,

- zieladresse und quelladresse, zwei 48-Bit Adressen, die Ethernet-Adressen darstellen und den Empfänger und den Sender des Pakets angeben,

- schluessel, eine 16-Bit-Folge, welche entweder ein high-level-Protokoll angibt oder die Länge der eigentlichen Nachricht codiert,

- nachricht, die eigentliche Nachricht, die in einer Folge der Länge 348 abgespeichert wird das IEEE-Format 802.3 schreibt vor, dass die Nachricht mindestens 368 Bit und höchstens 12 000 Bit lang sein darf und

- crc, eine 32-Bit CRC-Prüfsumme zum Erkennen von Übertragungsfehlern.

Der Zugriff auf eine einzelne Komponente eines Verbundes erfolgt über den Namen der Variablen, des Signals oder der Konstante gefolgt von einem Punkt und dem Namen der Komponente. So bezeichnet

```

ethernet_paket.zieladresse

```

die Komponente zieladresse des Signals ethernet\_paket und die Anweisung

```

26 ethernet_paket.zieladresse <= X"08002BE4B102";</pre>

```

weist dem in dem Signal ethernet\_paket abgespeicherten Paket eine Zieladresse zu.

Wie bei Feldern kann ein Verbund auch als Ganzes beschrieben werden. Hier bieten sich wie bei Feldern verschiedene Möglichkeiten in VHDL an, beispielsweise die Zuordnung der Werte zu den Komponenten über die Position,

```

28 ethernet_paket <=

29 ( syn, ziel, quelle, key, nachrichtentext, pruefsumme );</pre>

```

<sup>&</sup>lt;sup>6</sup> Eine schöne Einführung zu der Thematik der Computer-Netzwerke findet man in [38].

wobei syn, ziel, quelle, key, nachrichtentext und pruefsumme entsprechend definierte Vektoren sind. Die Zuordnung kann auch über die Namen der Komponenten erfolgen.

```

31   ethernet_paket <=

32   ( quelladresse => quelle, nachricht => nachrichtentext,

33         zieladresse => ziel, schluessel => key,

34         praeambel => syn, crc => pruefsumme );

```

Die Verwendung des Schlüsselwortes others

```

36    ethernet_paket <=

37    ( nachricht => nachrichtentext, schluessel => key,

38         praeambel => syn, crc => pruefsumme,

39         others => X"000000000000" );

```

steht ebenfalls zu Verfügung und weist allen noch nicht belegten Komponenten *einen* Wert zu. Das soeben verwendete **others**-Konstrukt übergibt an die beiden Komponenten zieladresse und quelladresse des Verbundes ethernet\_paket den Null-Vektor.

#### Fallstrick 8